# ANNAMACHARYA INSTITUTE OF TECHNOLOGY AND SCIENCES

# AUTONOMOUS)

Approved by AICTE, New Delhi & Permanent Affiliation to JNTUA, Anantapur.

Three B. Tech Programmes (CSE, ECE & CE) are accredited by NBA, New Delhi, Accredited by NAAC with 'A' Grade, Bangalore.

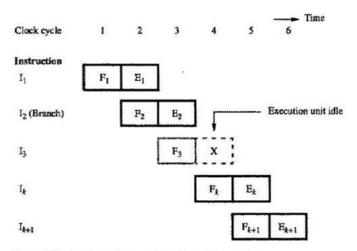

A-grade awarded by AP Knowledge Mission. Recognized under sections 2(f) & 12(B) of UGC Act 1956.

Venkatapuram Village, Renigunta Mandal, Tirupati, Andhra Pradesh-517520.

# **Department of Computer Science and Engineering**

Academic Year 2023-24

II. B.Tech I Semster

(AIDS)

**COMPUTER ORGANIZATION**

(20APC3007)

# **Prepared By**

Mrs.S.Venkata lakshmi., M.Tech(Ph.D). Assistant Professor Department of CSE, AITS

# ANNAMACHARYA INSTITUTE OF TECHNOLOGY AND SCIENCES::TIRUPATI(AUTONOMOUS)

Year: II Semester: I Branch of Study: AI & DS

| COURSE CODE | COURSE TITLE                                     | L | Т | P | CREDITS |

|-------------|--------------------------------------------------|---|---|---|---------|

| 20APC3007   | Computer Organization (Common to: CSE, CIC, & DS | 3 | 0 | 0 | 3       |

#### **COURSE OUTCOMES:**

After completion of the course, students will be able:

**CO1:** To Represent numbers and perform arithmetic operations.

**CO2:** To Minimize the Boolean expression using Boolean algebra and design it using logic gates

**CO3:** To Analyze and design combinational circuit.

**CO4:** To Design and develop sequential circuits

**CO5:** To Understand and apply the working of different operations on binary numbers

# **UNIT - 1: Basic Structure of Computer, Machine Instructions and Programs**

**Basic Structure of Computer**: Computer Types, Functional Units, Basic operational Concepts, Bus Structure, Software, Performance

**Machine Instructions and Programs**: Numbers, Arithmetic Operations and Programs, Instructions and Instruction Sequencing, Addressing Modes, Basic Input/output Operations, Stacks and Queues, Subroutines, Additional Instructions.

# **UNIT - 2: Arithmetic, Basic Processing Unit**

**Arithmetic**: Addition and Subtraction of Signed Numbers, Design of Fast Adders, Multiplication of Positive Numbers, Signed-operand Multiplication, Fast Multiplication, Integer Division, Floating-PointNumbers and Operations.

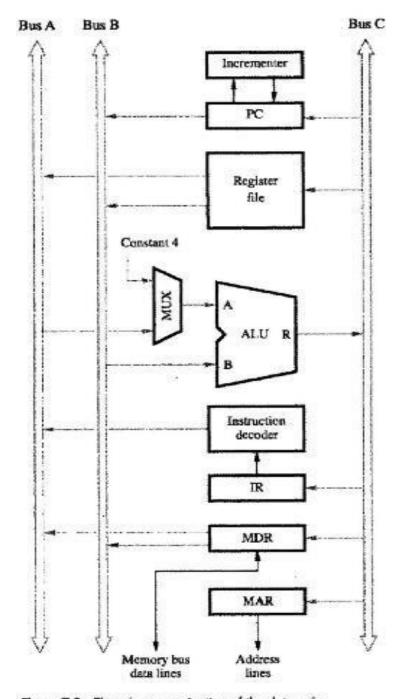

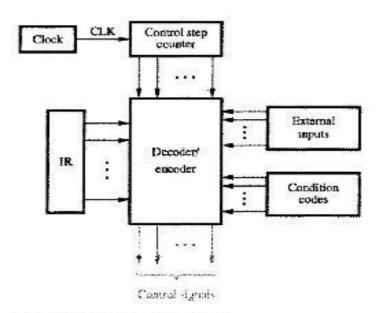

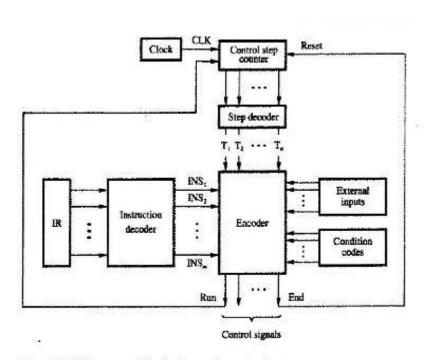

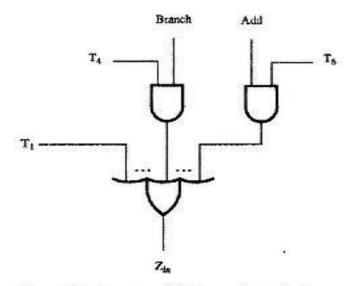

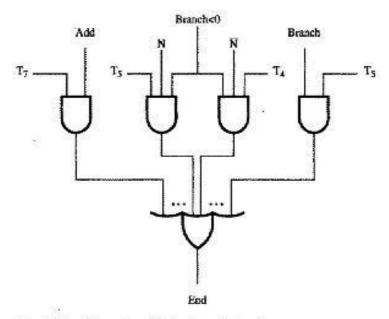

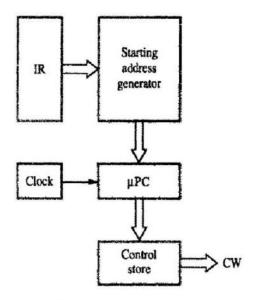

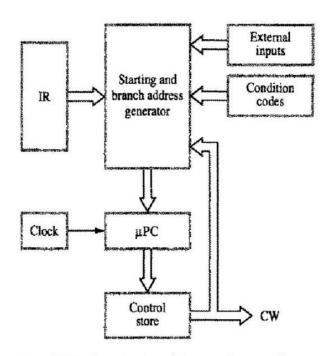

**Basic Processing Unit:** Fundamental Concepts, Execution of a Complete Instruction, Multiple-Bus Organization, HardwiredControl, and Multi programmed Control.

# UNIT - 3: The Memory System, Input/Output Organization

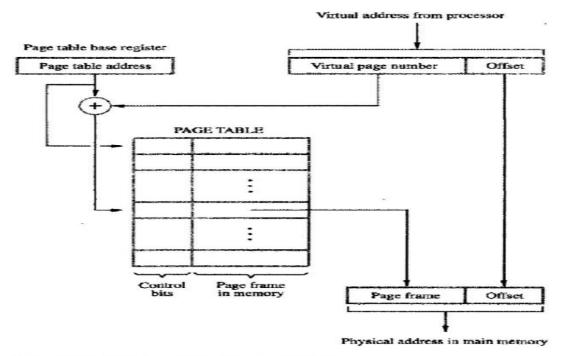

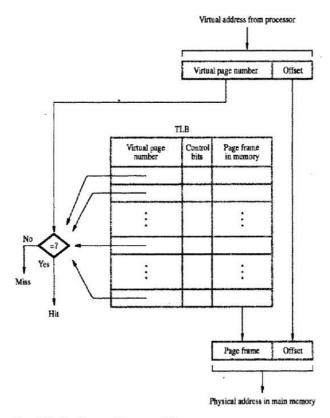

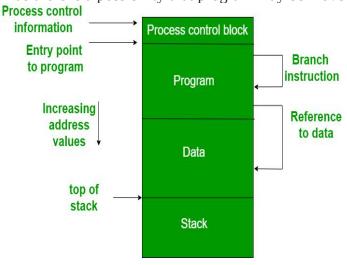

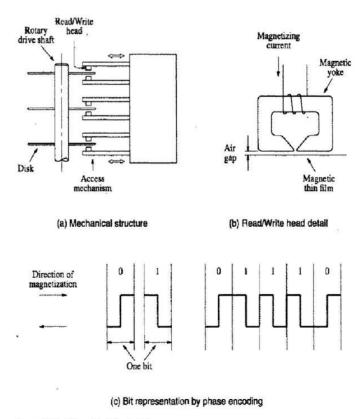

The Memory System: Basic Concepts, Semiconductor RAM Memories, Read-Only Memories, Speed, Size and Cost, CacheMemories, Performance Considerations, Virtual Memories, Memory Management Requirements, Secondary Storage.

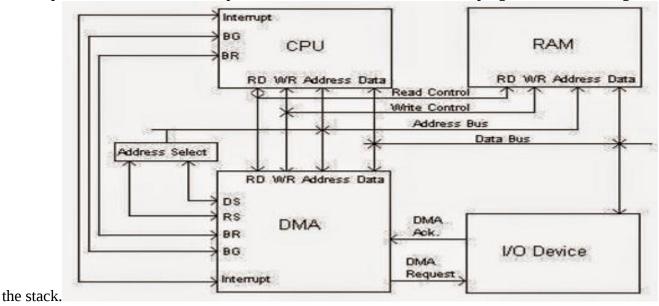

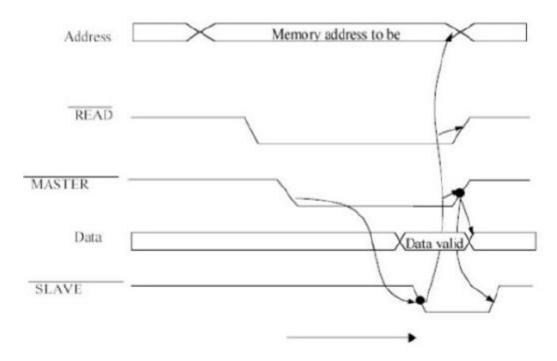

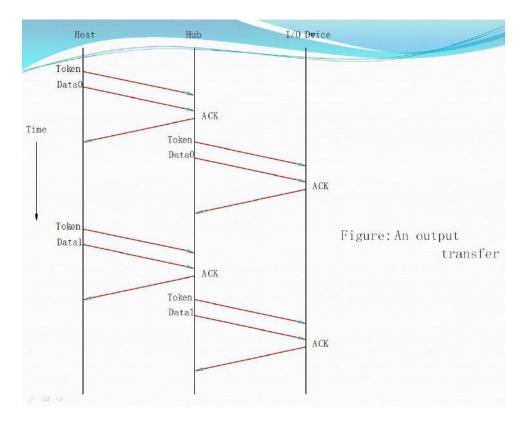

Input/Output Organization: Accessing I/O Devices, Interrupts, Processor Examples, Direct MemoryAccess, Buses, Interface Circuits, Standard I/O Interfaces.

# **UNIT - 4: Pipelining, Large Computer Systems**

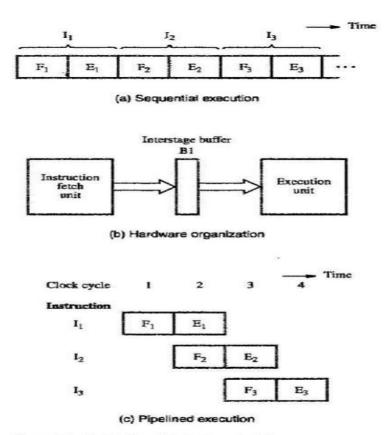

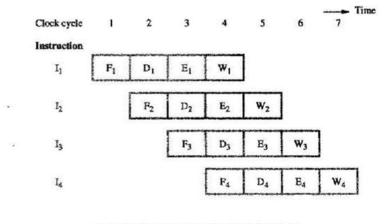

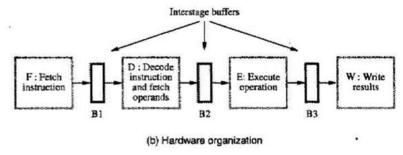

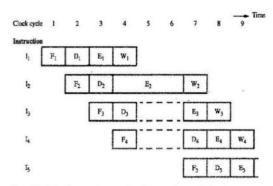

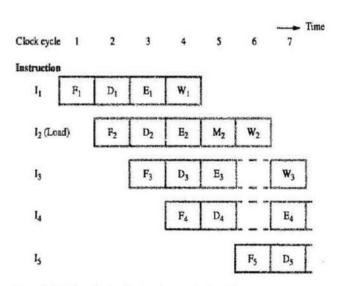

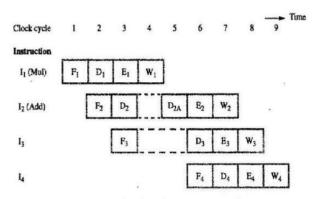

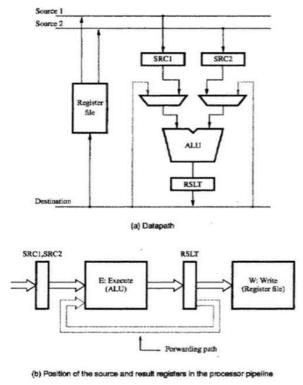

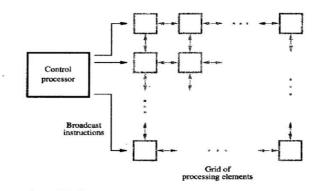

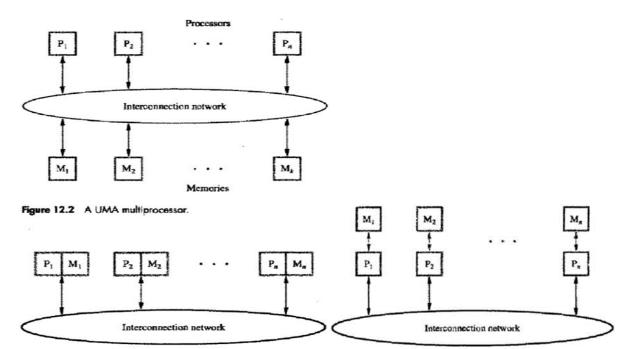

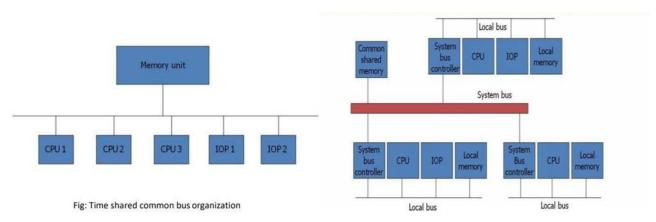

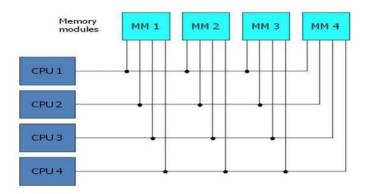

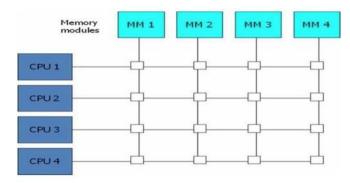

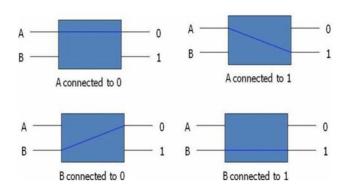

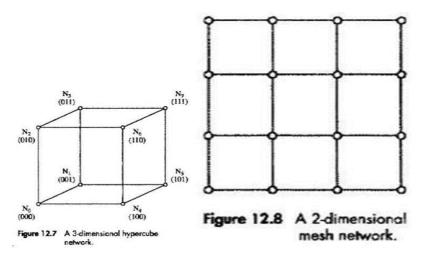

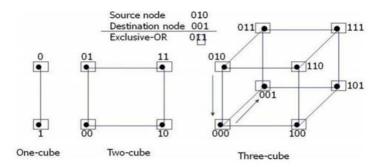

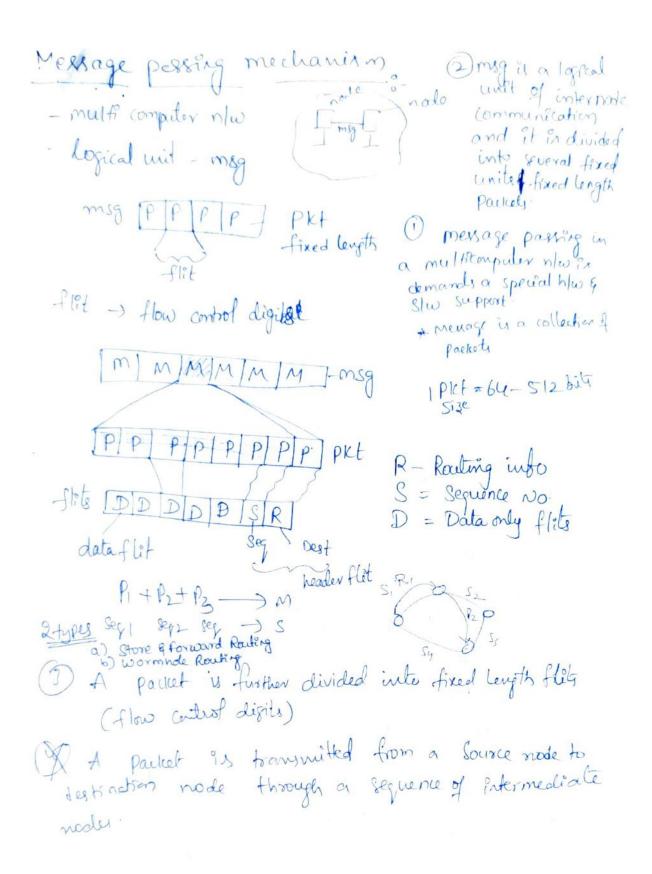

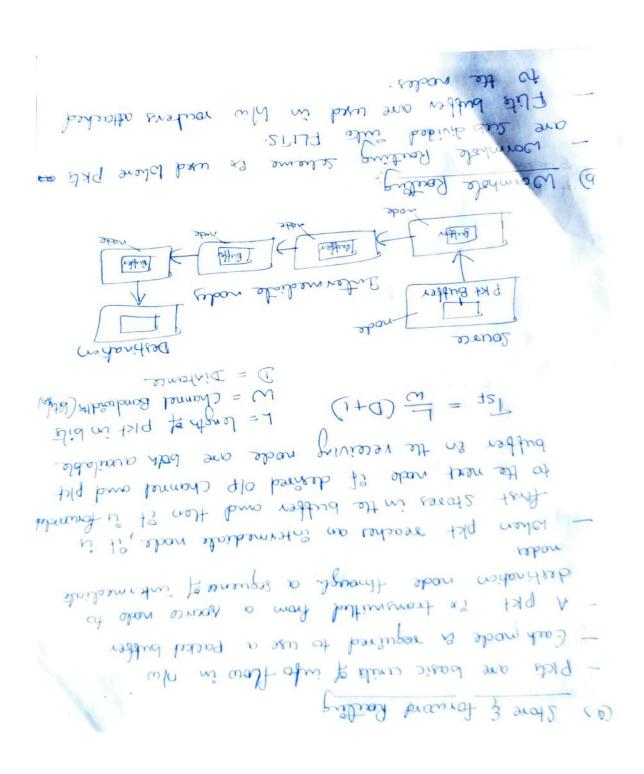

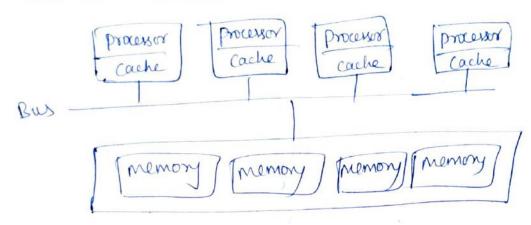

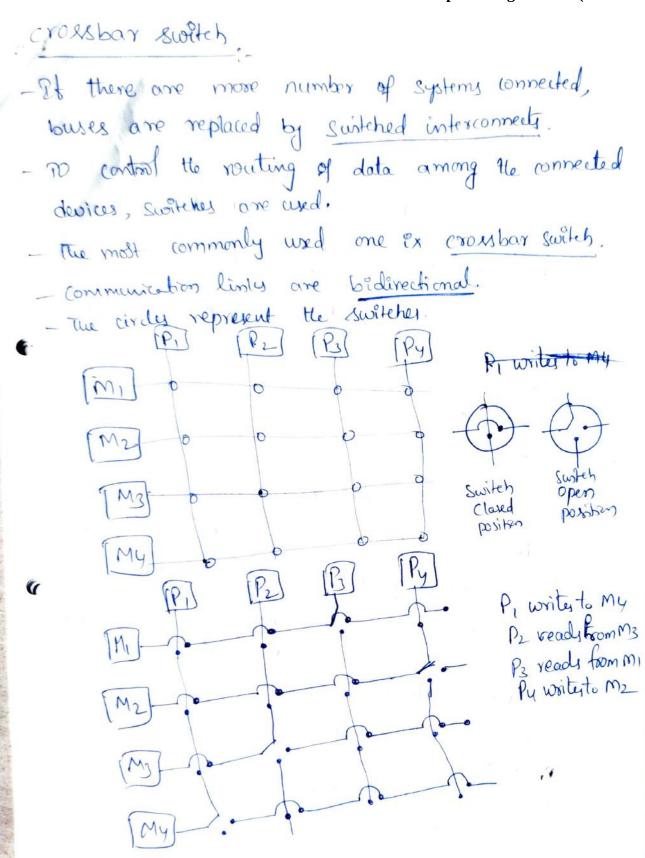

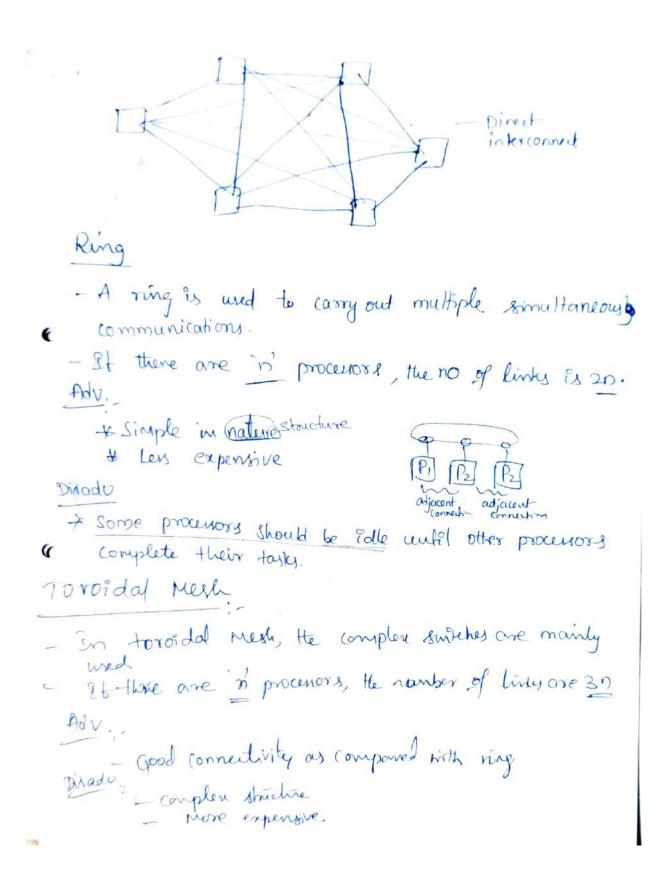

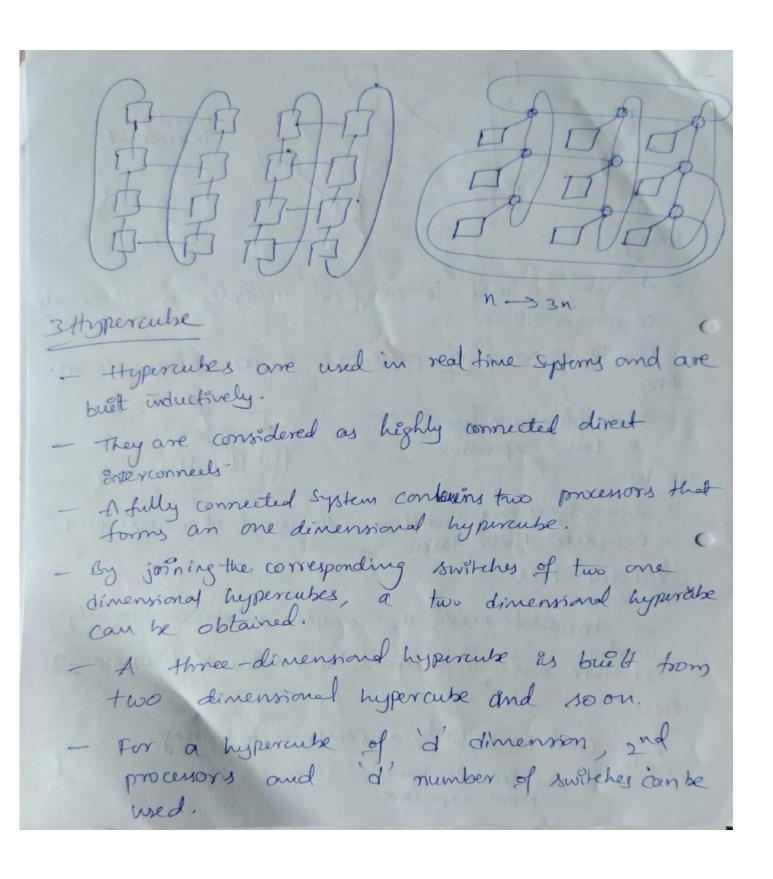

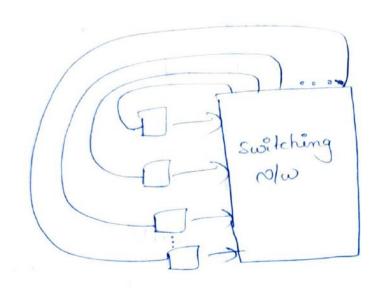

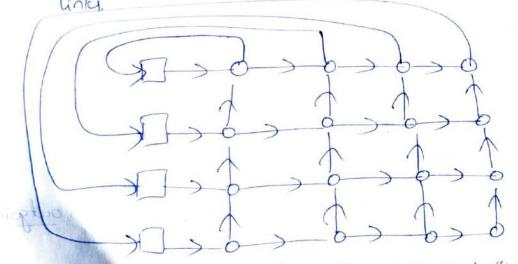

Pipelining: Basic Concepts, Data Hazards, Instruction Hazards, Influence on Instruction Sets Large Computer Systems: Forms of Parallel Processing, Array Processors, The Structure of General-Purpose multiprocessors, Interconnection Networks.

# **Unit -5: Computer Architecture**

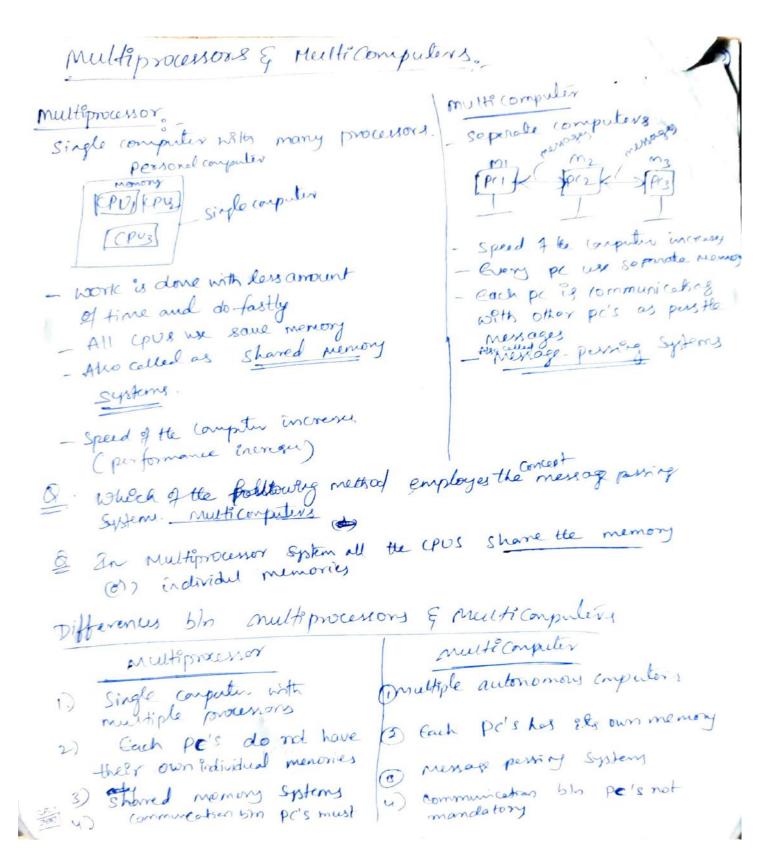

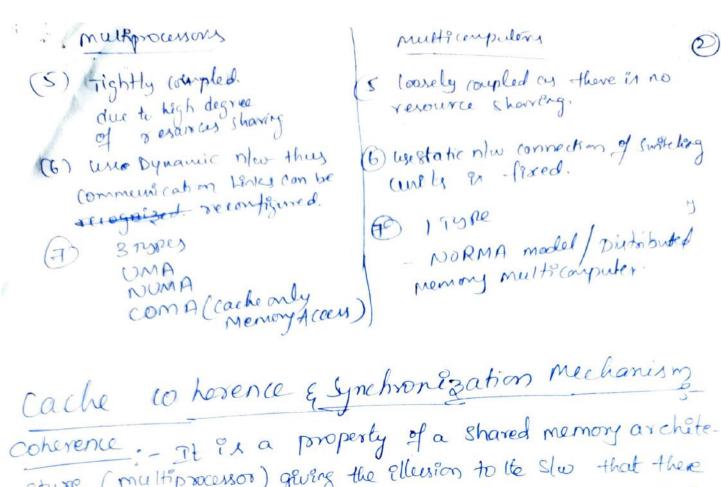

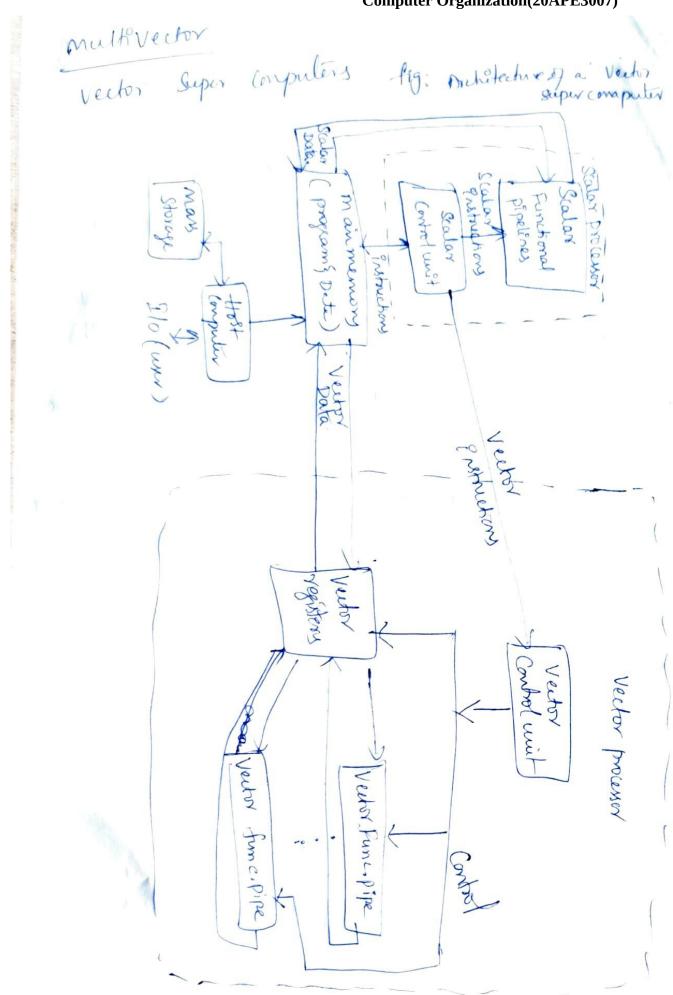

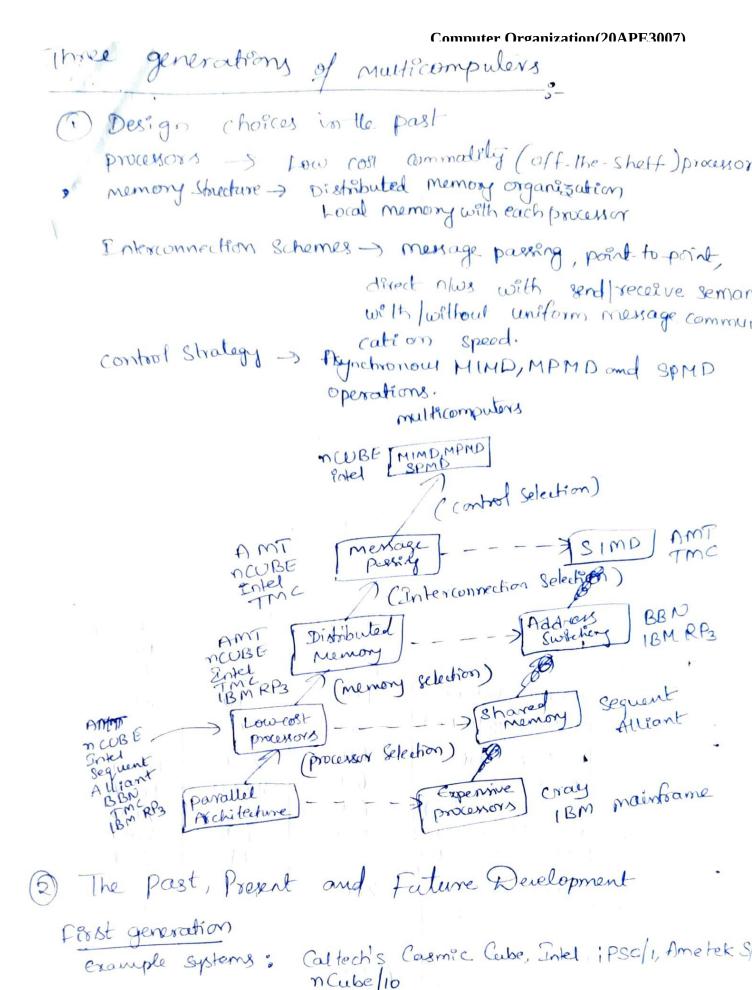

Parallel and Scalable Architectures, Multiprocessors and Multicomputers, cache coherence and synchronization mechanism, Three Generations of Multicomputers, Mechanisms, Multivetor and SIMD computers, Vector Processing Principals, Multivector Multiprocessors, Compound Vector processing, SIMD computer Organizations.

#### **Textbooks:**

- Carl Hamacher, ZvonkoVranesic, SafwatZaky, —Computer Organization II. 5th Edition, McGraw Hill Education, 2013.

- M.Morris Mano, —Computer System Architecturell, 3<sup>rd</sup> Edition, Pearson Education, 2017.

- Advanced Computer Architecture Second Edition, Kai Hwang, Tata McGraw Hill Publishers.

#### References

- 1. Themes and Variations, Alan Clements, —Computer Organization and Architecturell, CENGAGE Learning.

2. SmrutiRanjanSarangi, —Computer Organization and Architecturell, McGraw Hill

- Education.

- John P.Hayes, —Computer Architecture and Organization , McGraw Hill Education

# **Online Learning Resources:**

https://nptel.ac.in/courses/106/103/106103068/

# Mapping of course outcomes with program outcomes

|                 | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1             | 3   | 2   | 2   |     |     |     |     |     |     |      |      |      |      |      |

| CO <sub>2</sub> | 2   | 2   | 2   |     |     |     |     |     |     |      |      |      | 2    |      |

| CO <sub>3</sub> | 1   |     |     |     |     |     |     |     |     |      |      |      |      |      |

| CO <sub>4</sub> | 2   |     |     |     |     |     |     |     |     |      |      |      |      | 1    |

| CO <sub>5</sub> | 2   | 2   | 2   |     |     |     |     |     |     |      |      |      | 2    |      |

(Levels of Correlation, viz., 1-Low, 2-Moderate, 3 High)

#### **UNIT-I**

Basic Structure of Computer: Computer Types, Functional Units, Basic operational Concepts, Bus Structure, Software, Performance, Multiprocessors and Multicomputer.

Machine Instructions and Programs: Numbers, Arithmetic Operations and Programs, Instructions and Instruction Sequencing, Addressing Modes, Basic Input/output Operations, Stacks and Queues, Subroutines, Additional Instructions.

# **CHAPTER:1 Basic Structure of Computer**

#### Computer types

A computer can be defined as a fast electronic calculating machine that accepts the (data) digitized input information process it as per the list of internally stored instructions and produces the resulting information. List of instructions are called programs & internal storage is called computer memory.

The different types of computers are

- **1. Personal computers:** This is the most common type found in homes, schools, Business offices etc., It is the most common type of desk top computers with processing and storage units along with various input and output devices.

- **2. Note book computers:** These are compact and portable versions of PC

- **3. Work stations:** These have high resolution input/output (I/O) graphics capability, but with same dimensions as that of desktop computer. These are used in engineering applications of interactive design work.

- **4. Enterprise systems:** These are used for business data processing in medium to large corporations that require much more computing power and storage capacity than work stations. Internet associated with servers has become a dominant worldwide source of all types of information.

- **5. Super computers:** These are used for large scale numerical calculations required in the applications like weather forecasting etc.,

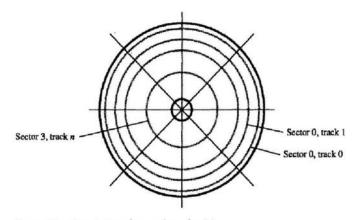

### Functional units:

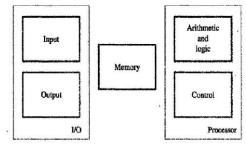

A computer consists of five functionally independent main parts input, memory, arithmetic logicunit (ALU), and output and control unit.

Figure 1.1 Basic functional units of a computer.

Input device accepts the coded information as source program i.e. high level language. This is either stored in the memory or immediately used by the processor to perform the desired operations. The program stored in the memory determines the processing steps. Basically the computer converts one source program to an object program. i.e. into machine language.

Finally the results are sent to the outside world through output device. All of these actions are coordinated by the control unit.

# Input unit: -

The source program/high level language program/coded information/simply data is fed to a computer through input devices keyboard is a most common type. Whenever a key is pressed, one corresponding word or number is translated into its equivalent binary code over a cable & fed either to memory or processor. Joysticks, trackballs, mouse, scanners etc are other input devices.

# Memory unit: -

Its function is to store programs and data. There are two classes of storage, they are:

# 1. Primary memory

# 2. Secondary memory

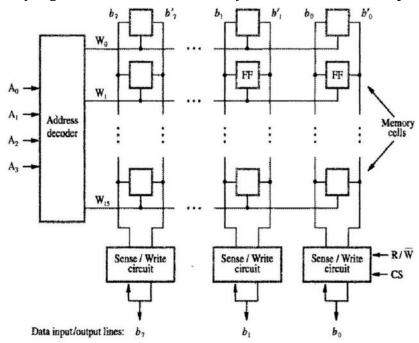

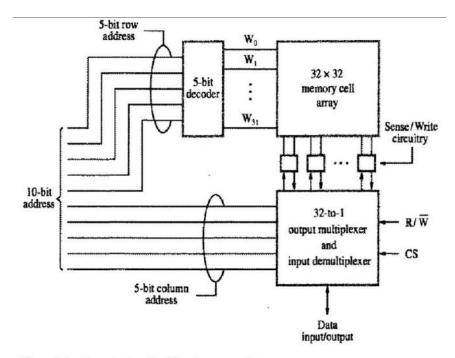

1. **Primary memory:** - Is the one exclusively associated with the processor and operates at the electronics speeds programs must be stored in this memory while they are being executed. The memory contains a large number of semiconductors storage cells, each capable of storing one bit of information. These cells are rarely read or written as individual cells but instead are processed in groups of fixed size called words.

To provide easy access to a word in memory, a distinct address is associated with each word location. **Addresses are** numbers that identify memory location. Number of bits in each word is called word length of the computer. Programs must reside in the memory during execution. Instructions and data can be written into the memory or read out under the control of processor.

Memory in which any location can be reached in a short and fixed amount of time afterspecifying its address is called random-access memory (RAM).

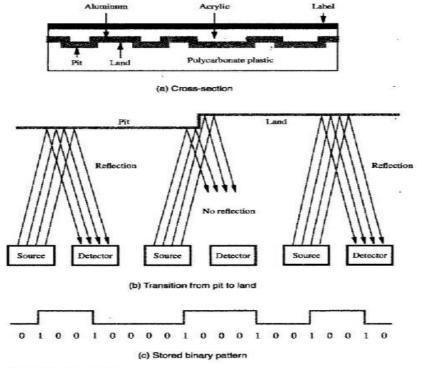

The time required to access one word in called memory access time. Memory which is only readable by the user and contents of which can't be altered is called read only memory (ROM) it contains operating system.

Caches are the small fast RAM units, which are coupled with the processor and are often contained on the same IC chip to achieve high performance. Although primary storage isessential it tends to be expensive.

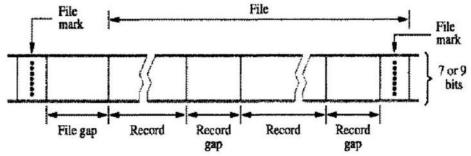

**2. Secondary Memory:** - Is used where large amounts of data & programs have to be stored, particularly information that is accessed infrequently.

**Examples:** Magnetic disks & tapes, optical disks (ie CD-ROM's), floppies etc.,

Arithmetic logic unit (ALU):-

Most of the computer operators are executed in ALU of the processor like addition, subtraction, division, multiplication, etc. the operands are brought into the ALU from memory and stored in high speed storage elements called register. Then according to the instructions the operation is performed in the required sequence.

The control and the ALU are many times faster than other devices connected to a computer system. This enables a single processor to control a number of external devices such as key boards, displays, magnetic and optical disks, sensors and other mechanical controllers.

# Output unit:-

These actually are the counterparts of input unit. Its basic function is to send the processed results to the outside world.

**Examples:** Printer, speakers, monitor etc.,

#### Control unit:-

It effectively is the nerve center that sends signals to other units and senses their states. The actual timing signals that govern the transfer of data between input unit, processor, memory and output unit are generated by the control unit.

The operation of a computer can be summarized as follows:

- The computer accepts information in the form of programs and data through an input unitand stores it in the memory.

- Information stored in the memory is fetched, under program control, into an arithmeticand logic unit, where it is processed.

- Processed information leaves the computer through an output unit.

- All activities inside the machine are directed by the control unit.

# Basic operational concepts

To perform a given task an appropriate program consisting of a list of instructions is stored in thememory. Individual instructions are brought from the memory into the processor, which executes the specified operations. Data to be stored are also stored in the memory.

# Examples: - Add LOCA, R0

This instruction adds the operand at memory location LOCA, to operand in register R0 & places the sum into register.

The original contents of location LOCA are preserved, whereas those of RO are overwritten. This instruction requires the performance of several steps,

- 1. First the instruction is fetched from the memory into the processor.

- 2. The operand at LOCA is fetched and added to the contents of R0

- 3. Finally the resulting sum is stored in the register R0

The preceding **Add** instruction combines a memory access operation with an ALU Operations. In some other type of computers, these two types of operations are performed by separateinstructions for performance reasons.

# Load LOCA, R1Add R1, R0

The first of these instructions transfers the contents of memory location **LOCA** into processor register **R1**, and the second instruction adds the contents of registers **RI** and **RO** and places the sum into **RO**.

Transfers between the memory and the processor are started by sending the address of the memory location to be accessed to the memory unit and issuing the appropriate control signals. The data are then transferred to or from the memory.

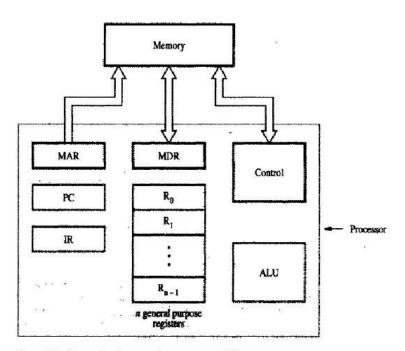

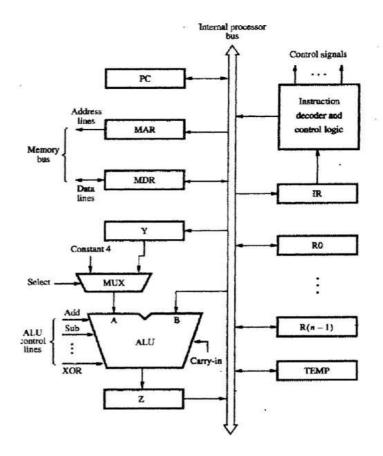

Figure 1.2 Connections between the processor and the memory.

The fig shows how memory & the processor can be connected. In addition to the ALU & the control circuitry, the processor contains a number of registers used for several different purposes.

**The instruction register (IR):-** Holds the instruction that is currently being executed. Its output is available for the control circuits which generates the timing signals that control the various processing elements in one execution of

instruction.

# The program counter PC:-

This is another specialized register that keeps track of execution of a program. It contains thememory address of the next instruction to be fetched and executed. Besides **IR** and **PC**, there are

n-general purpose registers R0 through Rn-1.

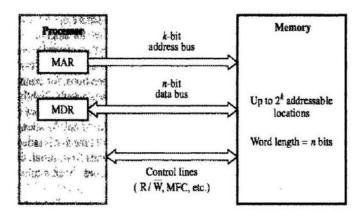

The other two registers which facilitate communication with memory are:

- **1. MAR (Memory Address Register):-** It holds the address of the location to be accessed.

- **2. MDR (Memory Data Register):** It contains the data to be written into or read out of theaddress location.

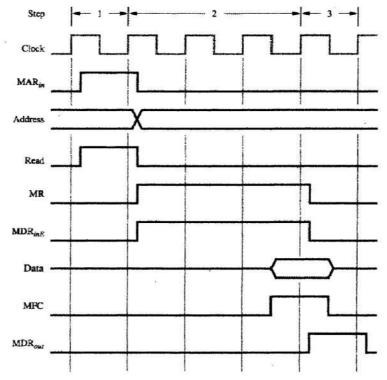

# Operating steps are

- 1. Programs reside in the memory & usually get these through the Input unit.

- 2. Execution of the program starts when the PC is set to point at the first instruction of theprogram.

- 3. Contents of PC are transferred to MAR and a Read Control Signal is sent to the memory.

- 4. After the time required to access the memory elapses, the address word is read out of thememory and loaded into the MDR.

- 5. Now contents of MDR are transferred to the IR & now the instruction is ready to be decoded and executed.

- 6. If the instruction involves an operation by the ALU, it is necessary to obtain the required operands.

- 7. An operand in the memory is fetched by sending its address to MAR & Initiating a readcycle.

- 8. When the operand has been read from the memory to the MDR, it is transferred from MDR to the ALU.

- 9. After one or two such repeated cycles, the ALU can perform the desired operation.

- 10. If the result of this operation is to be stored in the memory, the result is sent to MDR.

- 11. Address of location where the result is stored is sent to MAR & a write cycle is initiated.

- 12. The contents of PC are incremented so that PC points to the next instruction that is to be executed.

Normal execution of a program may be preempted (temporarily interrupted) if some devices require urgent servicing, to do this one device raises an Interrupt signal.

An interrupt is a request signal from an I/O device for service by the processor. The processor provides the requested service by executing an appropriate interrupt service routine.

The Diversion may change the internal stage of the processor its state must be saved in the memory location before interruption. When the interrupt-routine service is completed the state of the processor is restored so that the interrupted program may continue.

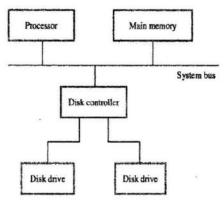

#### **BUS STRUCTURES**

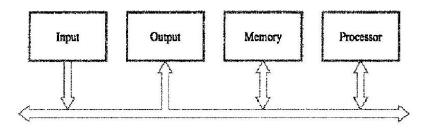

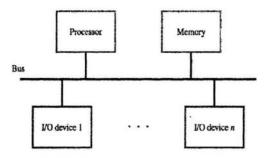

To achieve a reasonable speed of operation, a computer must be organized so that all its units can handle one full word of data at a given time. A group of lines that serve as a connecting port for several devices is called a **bus**.

'The simplest way to interconnect functional units is to use a single bus, as shown in *Figure 1.3*. Ail units are Department of CSE,AITS-TIRUPATI 7

connected to this bus. Because the bus can be used for only one transfer at a time, only two units can actively use the bus at any given time. Bus control lines are used to arbitrate multiple requests for use of one bus.

Figure 1.3 Single-bus structure.

# Single bus structure is

- Low cost

- Very flexible for attaching peripheral devices

Multiple bus structure certainly increases the performance but also increases the costsignificantly.

All the interconnected devices are not of same speed & time leads to a bit of a problem. This is solved by using cache registers (ie buffer registers). These buffers are electronic registers of small capacity when compared to the main memory but of comparable speed.

The instructions from the processor at once are loaded into these buffers and then the completetransfer of data at a fast rate will take place.

#### Software

System software is a collection of programs that are executed as needed to perform functions such as,

- ② Receiving and interpreting user commands

- ② Entering and editing application programs and storing them as files in secondary storagedevices

- Managing the storage and retrieval of files in secondary storage devices

- © Running standard application programs such as word processors, spreadsheets, or games, with data supplied by the user

- ① Controlling 1/O units to receive input information and produce output results

- Translating programs from source form prepared by the user into object form consisting of machine instructions

- ① Linking and running user-written application programs with existing standard libraryroutines, such as numerical computation packages

System software is thus responsible for the coordination of all activities in a computing system. Application programs are usually written in a high-level programming language, such as C, C++, Java, or FORTRAN, in which the programmer specifies mathematical or text-processing operations.

A system software program called a **compiler** translates the high-level language program into asuitable machine

language program.

Another important system program is **Text editor**; it is used for entering and editing application programs. The user of this program interactively executes commands that allow statements of a source program entered at a keyboard to be accumulated in a file.

A **file** is simply a sequence of alphanumeric characters or binary data that is stored in memory or in secondary storage. A file can be referred to by a name chosen by the user.

# **Performance**

The most important measure of the performance of a computer is how quickly it can execute programs. The speed with which a computer executes program is affected by the design of its hardware. For best performance, it is necessary to design the compiles, the machine instruction set, and the hardware in a coordinated way.

The total time required to execute the program is elapsed time is a measure of the performance of the entire computer system. It is affected by the speed of the processor, the disk and the printer. The time needed to execute a instruction is called the processor time.

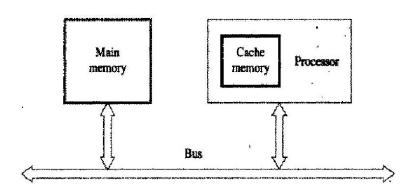

Just as the elapsed time for the execution of a program depends on all units in a computer system, the processor time depends on the hardware involved in the execution of individual machine instructions. This hardware comprises the processor and the memory which are usually connected by the bus as shown in the fig c.

Figure 1.5 The processor cache.

Let us examine the flow of program instructions and data between the memory and the processor. At the start of execution, all program instructions and the required data are stored in the main memory. As the execution proceeds, instructions are fetched one by one over the bus into the processor, and a copy is placed in the cache later if the same instruction or data item is needed a second time, it is read directly from the cache.

The processor and relatively small cache memory can be fabricated on a single IC chip. The internal speed of performing the basic steps of instruction processing on chip is very high and is considerably faster than the speed at which the instruction and data can be fetched from the mainmemory. A program will be executed faster if the movement of instructions and data between themain memory and the processor is minimized, which is achieved by using the cache.

For example: Suppose a number of instructions are executed repeatedly over a short period of time as happens in a program loop. If these instructions are available in the cache, they can be fetched quickly during the period of repeated use. The same applies to the data that are used repeatedly.

#### Processor clock:

Processor circuits are controlled by a timing signal called clock. The clock designer the regular time intervals called clock cycles. To execute a machine instruction the processor divides the action to be performed into a sequence of basic steps that each step can be completed in one clock cycle. The length P of one clock cycle is an important parameter that affects the processor performance.

Processor used in today's personal computer and work station has a clock rates that range from a few hundred million to over a billion cycles per second.

# CHAPTER-2 MACHINE INSTRUCTIONS AND PROGRAMS

# NUMBERS, ARITHMETIC OPERATIONS AND PROGRAMS

Computers are built using logic circuits that operate on information represented by two valued electrical signals. We label the two values as 0 and 1; and we define the amount of information represented by such a signal as a *bit* of information, where *bit* stands for *binary digit*. The most natural way to represent a number in a computer system is by a string of bits, called a *binary* number. A text character can also be represented by a string of bits called a *character code*.

#### NUMBER REPRESENTATION

Consider an n-bit vector

$B=b_{n-1} .... B_1b_0$

Where  $b_i=0$  or 1 for  $0 \le i \le n-1$ . This vector can represent unsigned integer values V in the range 0 to  $2^n$  -1, where

$$V(B) = b_{n-1} \times 2^{n-1} + \cdots + b_1 \times 2^1 + b_0 \times 2^0$$

We obviously need to represent both positive and negative numbers. Three systems are used for representing such numbers:

✓ Sign-and-magnitude

✓ 1's-complement ✓ 2's-complement

In all three systems, the leftmost bit is 0 for positive numbers and 1 for negative numbers. Fig

illustrates all three representations using 4-bit numbers. Positive values have identical representations in al systems, but negative values have different representations. In the *sign-and-magnitude* systems, negative values are represented

by changing the most significant bit (b3 in figure 2.1) from 0 to 1 in the B vector of the corresponding positive value. For example, +5 is represented by 0101, and -5 is represented by 1101.

| B                                                           | Values represented    |                |               |  |  |

|-------------------------------------------------------------|-----------------------|----------------|---------------|--|--|

| b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> | Sign and<br>magnitude | 1's complement | 2's complemen |  |  |

| 0111                                                        | +7                    | +7             | +7            |  |  |

| 0110                                                        | +6                    | +6             | +6            |  |  |

| 0101                                                        | +5                    | + 5            | + 5           |  |  |

| 0100                                                        | + 4                   | +4             | +4            |  |  |

| 0011                                                        | + 3                   | +3             | +3            |  |  |

| 0010                                                        | +2                    | + 2            | +2            |  |  |

| 0001                                                        | + 1                   | +1             | +1            |  |  |

| 0000                                                        | +0                    | +0             | +0            |  |  |

| 1000                                                        | -0                    | - 7            | -8            |  |  |

| 1001                                                        | - 1                   | -6             | -7            |  |  |

| 1010                                                        | -2                    | 5              | 6             |  |  |

| 1011                                                        | -3                    | -4             | -5            |  |  |

| 1100                                                        | -4                    | -3             | -4            |  |  |

| 1101                                                        | - 5                   | - 2            | -3            |  |  |

| 1110                                                        | -6                    | - i            | -2            |  |  |

| 1111                                                        | -7                    | -0             | -1            |  |  |

Figure 2.1 Binary, signed-integer representations.

In 1's- complement representation, negative values are obtained by complementing each bit of the corresponding positive number. Thus, the representation for -3 is obtained by complementingeach bit in the vector 0011 to yield 1100. Clearly, the same operation, bit complementing, is done in converting a negative number to the corresponding positive value. Converting either way is referred to as forming the 1's-complement of a given number. Finally, in the 2's-complement system, forming the 2's-complement of a number is done by subtracting that number from 2<sup>n</sup>. Hence, the 2's complement of a number is obtained by adding 1 to the 1's complement of that number.

#### Addition of Positive numbers:-

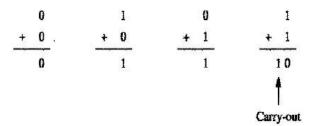

Consider adding two 1-bit numbers. The results are shown in figure 2.2. Note that the sum of 1 and 1 requires the 2-bit vector 10 to represent the value 2. We say that the sum is 0 and the carry-out is 1. In order to add multiple-bit numbers, we use a method analogous to that used for manual computation with decimal numbers. We add bit pairs starting from the low-order (right) and of the bit vectors, propagating carries toward the high-order (left) end.

Figure 2.2 Addition of 1-bit numbers.

# INSTRUCTIONS AND INSTRUCTION SEQUENCING

A computer must have instructions capable of performing four types of operations.

- Data transfers between the memory and the processor registers

- ② Arithmetic and logic operations on data

- Program sequencing and control

- ① I/O transfers

#### **REGISTER TRANSFER NOTATION:-**

Transfer of information from one location in the computer to another. Possible locations that may be involved in such transfers are memory locations that may be involved in such transfers are memory locations, processor registers, or registers in the I/O subsystem. Most of the time, weidentify a location by a symbolic name standing for its hardware binary address. For *Example*,

names for the addresses of memory locations may be LOC, PLACE, A, VAR2; processor

registers names may be **R0**, **R5**; and I/O register names may be **DATAIN**, **OUTSTATUS**, and so on. The contents of a location are denoted by placing square brackets around the name of the location. Thus, the expression

$$R1 \leftarrow [LOC]$$

Means that the contents of memory location **LOC** are transferred into processor register **R1**.

As another example, consider the operation that adds the contents of registers **R1** and **R2**, and then places their sum into register R3. This action is indicated as

$$R3 \leftarrow [R1] + [R2]$$

This type of notation is known as *Register Transfer Notation (RTN)*. Note that "the right-hand side of an RTN expression always denotes a value, and the left-hand side is the name of a location where the value is to be places, overwriting the old contents of that location".

#### ASSEMBLY LANGUAGE NOTATION:-

Assembly language format is another type of notation to represent machine instructions and programs. For example,

an instruction that causes the transfer described above, from memory location LOC to processor register R1, is specified by the statement

#### MOV LOC,R1

The contents of LOC are unchanged by the execution of this instruction, but the old contents of register R1 are overwritten.

The second example of adding two numbers contained in processor registers R1 and R2 and placing their sum in R3 can be specified by the assembly language statement

#### Add R1,R2,R3

#### **BASIC INSTRUCTIONS:**

The operation of adding two numbers is a fundamental capability in any computer. The statement

$$C = A + B$$

In a high-level language program is a command to the computer to add the current values of the two variables called A and B, and to assign the sum to a third variable, C. When the program containing this statement is compiled, the three variables, A, B, and C, are assigned to distinct locations in the memory. We will use the variable names to refer to the corresponding memory location addresses. The contents of these locations represent the values of the three variables. Hence, the above high-level language statement requires the action to take place in the computer.

$$C \leftarrow [A] + [B]$$

To carry out this action, the contents of memory locations  $\bf A$  and  $\bf B$  are fetched from the memory and transferred into the processor where their sum is computed. This result is then sent back to the memory and stored in location  $\bf C$ .

Let us first assume that this action is to be accomplished by a single machine instruction. Furthermore, assume that this instruction contains the memory addresses of the three operands, A, B, and C. This three-address instruction can be represented symbolically as

#### Add A,B,C

Operands A and B are called the *source operands*, C is called the *destination operand*, and Addis the operation to be performed on the operands. A general instruction of this type has the format

# Operation Source1, Source2, Destination

If k bits are needed for specify the memory address of each operand, the encoded form of the above instruction must contain 3k bits for addressing purposes in addition to the bits needed to denote the Add operation.

An alternative approach is to use a sequence of simpler instructions to perform the same task, with each instruction having only one or two operands. Suppose that two- address instructions of the form

Operation Source, Destination

are available. An Add instruction of this type is

Add A,B

which performs the operation  $\mathbf{B} \leftarrow [\mathbf{A}] + [\mathbf{B}]$ . When the sum is calculated, the result is sent to the

memory and stored in location B, replacing the original contents of this location. This means that operand B is both a *source* and a *destination*.

A single two-address instruction cannot be used to solve our original problem, which is to add the contents of locations A and B, without destroying either of them, and to place the sum in location C. The problem can be solved by using another two-address instruction that copies the contents of one memory location into another. Such an instruction is

Move B,C

Which performs the operations  $C \leftarrow [B]$ , leaving the contents of location B unchanged. Using only one-address instructions, the operation  $C \leftarrow [A] + [B]$  can be performed by two instruction sequence

Move B,CAdd A,C

Thus, the one-address instruction

Add A

means the following: Add the contents of memory location A to the contents of the accumulator register and place the sum back into the accumulator. Let us also introduce the one-address instructions

Load A

and

## store A

The Load instruction copies the contents of memory location A into the accumulator, and the Store instruction copies the contents of the accumulator into memory location A. Using only one-address instructions, the operation  $C \leftarrow [A] + [B]$  can be performed by executing the sequence of instructions

Load A Add B

Store C

Some early computers were designed around a single accumulator structure. Most moderncomputers have a number of general-purpose processor registers – typically 8 to 32, and even considerably more in some cases. Access to data in these registers is much faster than to data stored in memory locations because the registers are inside the processor.

Let Ri represent a general-purpose register. The instructions

Department of CSE, AITS-TIRUPATI

# Load A, Ri Store Ri, A and Add A, Ri

Are generalizations of the Load, Store, and Add instructions for the single-accumulator case, in which register Ri performs the function of the accumulator.

When a processor has several general-purpose registers, many instructions involve only operands that are in the register. In fact, in many modern processors, computations can be performed directly only on data held in processor registers. Instructions such as

Add Ri, Rj Or

Add Ri, Rj, Rk

In both of these instructions, the source operands are the contents of registers  $R_i$  and  $R_j$ . In the first instruction,  $R_j$  also serves as the destination register, whereas in the second instruction, a third register,  $R_k$ , is used as the destination.

It is often necessary to transfer data between different locations. This is achieved with the instruction

#### Move Source, Destination

When data are moved to or from a processor register, the Move instruction can be used rather than the Load or Store instructions because the order of the source and destination operands determines which operation is intended. Thus,

Move A, Ri Is the same as

And

Load A, Ri

Move Ri, A

Is the same as Store Ri, A

In processors where arithmetic operations are allowed only on operands that are processor registers, the C = A + B task can be performed by the instruction sequence

Move A, Ri Move B, Rj Add Ri, Rj Move Rj, C

In processors where one operand may be in the memory but the other must be in register, an instruction sequence for the required task would be

Department of CSE, AITS-TIRUPATI

Move A, Ri

Add B, Ri Move Ri, C

The speed with which a given task is carried out depends on the time it takes to transfer instructions from memory into the processor and to access the operands referenced by these instructions. Transfers that involve the memory are much slower than transfers within the processor.

We have discussed three-, two-, and one-address instructions. It is also possible to use instructions in which the locations of all operands are defined implicitly. Such instructions are found in machines that store operands in a structure called a pushdown stack. In this case, the instructions are called zero-address instructions.

# INSTRUCTION EXECUTION AND STRAIGHT-LINE SEQUENCING:

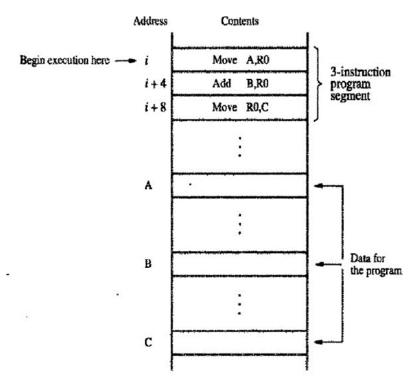

The three instructions of the program are in successive word locations, starting at location i. Since each instruction is 4 bytes long, the second and third instructions start at addresses i + 4 and i + 8.

Let us consider how below program is executed. The processor contains a register called the program counter (PC), which holds the address of the instruction to be executed next.

To begin executing a program, the address of its first instruction (i in our example) must be placed into the PC. Then, the processor control circuits use the information in the PC to fetch and execute instructions, one at a time, in the order of increasing addresses. This is called straight-line sequencing. During the execution of each instruction, the PC is incremented by 4 to point to the next instruction. Thus, after the Move instruction at location i + 8 is executed, the PC

contains the value i + 12, which is the address of the first instruction of the next program segment

Figure 2.8 A program for  $C \leftarrow [A] + [B]$ .

Executing a given instruction is a two-phase procedure: instruction fetch & instruction execute.

In the first phase the instruction is fetched from the memory location whose address is in the PC. This instruction is placed in the instruction register (IR) in the processor.

At the start of the second phase the instruction in IR is examined to determine which operation is to be performed.

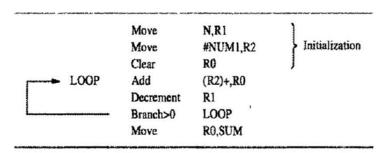

#### **BRANCHING:**

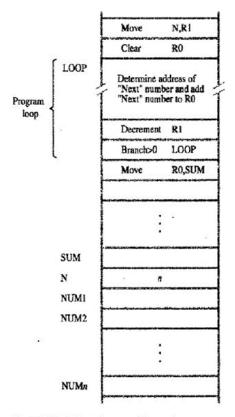

Consider the task of adding a list of n numbers. The addresses of the memory locations containing the n numbers are symbolically giver as NUM1, NUM2... NUMn and a separate Add

instruction is used to add each number to the contents of register R0. After all the numbers have been added, the result is placed in memory location SUM.

The loop is a straight-line sequence of instructions executed as many times as needed. It starts at location LOOP and ends at the instruction Branch>0. During each pass through this loop, the address of the next list entry is determined, and that entry is fetched and added to RO.

Assume that the number of entries in the list, 2, is stored in memory location N. Register R1 is used as a counter to determine the number of times the loop is executed. Hence, the contents of location N are leaded into register R1 at the beginning of the program. Then, within the body of the loop, the instruction

#### Decrement R1

reduces the contents of RI by 1 each time through the Loop. Execution of the loop is repeated as long as the result of the decrement operation is greater than zero.

Branch instruction loads a new value into the program counter. The processor fetches and executes the instruction at this new address, called the branch target. Conditional branch instruction causes a branch only if a specified condition is satisfied. If the condition is not satisfied, the PC is incremented in the normal way, and the next instruction in sequential address order is fetched and executed.

## Branch>0 LOOP

Figure 2.10 Using a loop to add n numbers.

The Move instruction is fetched and executed. It moves the final result from R0 into memory location SUM. CONDITION CODES:

The processor keeps track of information about the results of various operations for use by subsequent conditional branch instructions. This is accomplished by recording the required information in individual bits, often called condition code flags. These flags are usually grouped together in a special processor register called the condition code register or status register.

Individual condition code flags are set to 1 or cleared to 0, depending on the outcome of the operation performed.

Four commonly used flags are:

N (negative) Set to 1 if the result is negative; otherwise, cleared to 0 Z (zero) Set to 1 if the result is 0; otherwise, cleared to 0

V (overflow) Set to 1 if arithmetic overflow occurs; otherwise, cleared to 0

C (carry) Set to 1 if a carry-out results from the operation; otherwise, cleared to 0

The N and Z flags indicate whether the result of an arithmetic or logic operation is negative or zero. The N and Z flags may also be affected by instructions that transfer data, such as Move, Load, or Store.

The V flag indicates whether overflow has taken place. The processor sets the V flag to allow the programmer to test whether overflow has occurred and branch to an appropriate routine that corrects the problem. Instructions such as BranchlfOverflow are provided for this purpose.

The C flag is set to 1 if a carry occurs from the most significant bit position during an arithmetic operation. This flag makes it possible to perform arithmetic operations on operands that are longer than the word length of the processor.

The instruction Branch>0, tests one or more of the condition flags.

## GENERATING MEMORY ADDRESSES:

Suppose that a processor register, Ri, is used to hold the memory address of an operand, H it is initially loaded with the address NUM1 before the loop is entered and is then incremented by 4 on each pass through the loop, it can provide the needed capability.

#### ADDRESSING MODES:

The different ways in which the location of an operand is specified in an instruction are referred to as addressing modes.

Table 2.1 Generic addressing modes

| Name                          | Assembler syntax | Addressing function               |

|-------------------------------|------------------|-----------------------------------|

| Immediate                     | #Value           | Operand = Value                   |

| Register                      | Ri               | EA = Ri                           |

| Absolute (Direct)             | LOC              | EA = LOC                          |

| Indirect                      | (Ri)<br>(LOC)    | $EA = \{Ri\}$<br>$EA = \{LOC\}$   |

| Index                         | X(RI)            | $EA = \{Ri\} + X$                 |

| Base with index               | (Ri,Rj)          | EA = [Ri] + [Rj]                  |

| Base with index<br>and offset | X(Ri,Rj)         | EA = [Ri] + [Rj] + i              |

| Relative                      | X(PC)            | EA = [PC] + X                     |

| Autoincrement                 | (Ri)+            | EA = [Ri];<br>Increment Ri        |

| Autodecrement                 | -(Ri)            | Decrement $Ri$ ;<br>$EA = \{Ri\}$ |

EA = effective address Value = a signed number

#### IMPLEMENTATION OF VARIABLES AND CONSTANTS:

Variables and constants are the simplest data types and are found in almost every computer program. In assembly language, a variable is represented by allocating a register or a memory location to hold its value. Thus, the value can be changed as needed using appropriate instructions.

Register mode: The operand is the contents of a processor register; the name (address) of the register is given in the instruction.

Absolute mode: The operand is in a memory location; the address of this location is given explicitly in the instruction. (In some assembly languages, this mode is called Direct.)

The instruction

#### MOVE LOC, R2

uses these two modes. Processor registers are used as temporary storage locations where the data in a register are accessed using the Register mode. The Absolute mode can represent global variables in a program. A declaration such as

Integer A, B;

in a high-level language program will cause the compiler to allocate a memory location to each of the variables A and B.

Immediate mode: The operand is given explicitly in the instruction.

For example, the instruction

Move 200immediae, R0

places the value 200 in register R0.

The Immediate mode is only used to specify the value of a source operand.

A common convention is to use the sharp sign (#) in front of the value to indicate that this value is to be used as an immediate operand.

Move #200, R0

Constant values are used frequently in high-level language programs. For example, the statement

A=B+6

contains the constant 6, Assuming that A and B have been declared earlier as variables and may be accessed using the Absolute mode, this statement may be compiled as follows:

Move B,R1

Add #6,R1

Move R1,A

INDIRECTION AND POINTERS

In the addressing modes that follow, the instruction provides information from which the memory address of the operand can be determined. We refer to this address as the effective address (EA) of the operand.

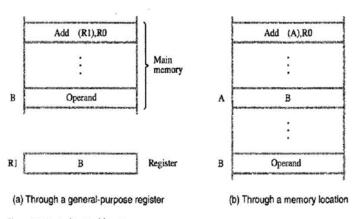

Indirect mode: The effective address of the operand is the contents of a register or memory location whose address appears in the instruction.

Indirection will be denoted by placing the name of the register or the memory address given in the instruction in parentheses.

To execute the Add instruction in Figure 2.11a, the processor uses the value B, which is in register R1, as the effective address of the operand. It requests a read operation from the memory to read the contents of location B. The value read is the desired operand, which the processor adds to the contents of register R0. Indirect addressing through a memory location is also possible as shown in Figure 2.11b. In this case, the processor first reads the contents of memory location A, and then requests a second read operation using the value B as an address to obtain the operand.

Figure 2.11 Indirect addressing.

The register or memory location that contains the address of an operand is called a pointer.

For adding a list of numbers, indirect addressing can be used to access successive numbers in the list, resulting in the program shown in Figure 2.12. Register R2 is used as a pointer to the numbers in the list, and the operands are accessed indirectly through R2. The initialization section of the program loads the counter value n from memory location N into R1 and uses the immediate addressing mode to place the address value NUM1, which is the address of the first number in the list, into R2. Then it clears R0 to 0. The first time through the loop, the instruction

Add (R2),R0

fetches the operand at location NUMI and adds it to R0. The second Add instruction adds 4 to the contents of the pointer R2, so that it will contain the address value NUM2 when the above instruction is executed in the second pass through the loop.

Consider the C-language statement

A=\*B

where B is a pointer variable. This statement may be compiled into

Move B,R1 Move (R1),A

Using indirect addressing through memory, the same action can be achieved with

Department of CSE, AITS-TIRUPATI

Move (B),A

**INDEXING AND ARRAYS:**

It is useful in dealing with lists and arrays.

Index mode: The effective address of the operand is generated by adding a constant value to the contents of a register.

The register used may be either a special register provided for this purpose, or, more commonly, it may be any one of a set of general-purpose registers in the processor. In either case, it is referred to as an index register.

Index mode can be indicated symbolically as

X(Ri)

where X denotes the constant value contained in the instruction and Ri is the name of the register involved. The effective address of the operand is given by

$$EA = X + [Ri]$$

The contents of the index register are not changed in the process of generating the effective address.

In an assembly language program, the constant X may be given cither as an explicit number or as a symbolic name representing a numerical value.

In Figure 2.13a, the index register, Ri, contains the address of a memory location, and the value X defines an offset (also called a displacement) from this address to the location where the operand is found.

An alternative use is illustrated in Figure 2.13b. Here, the constant X corresponds to a memory address, and the contents of the index register define the offset to the operand.

In either case, the effective address is the sum of two values; one is given explicitly in the instruction, and the other is stored in a register.

Figure 2.13 Indexed addressing.

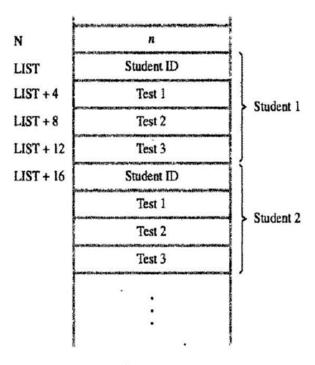

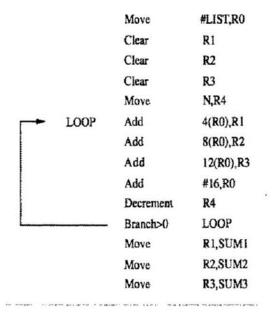

To see the usefulness of indexed addressing, consider a simple example involving a list of test scores for students taking a given course. Assume that the list of scores, beginning at location LIST, is structured as shown in Figure 2.14. A four-word memory block comprises a record that stores the relevant information for each student. Each record consists of the student's identification number (ID), followed by the scores the student earned on three tests. There are n students in the class, and the value n is stored in location N immediately in front of the list. The addresses given in the figure for the student IDs and test scores assume that the memory is byte addressable and that the word length is 32 bits

Each row contains the entries for one student, and the columns give the IDs and test scores.

In general, the Index mode facilitates access to an operand whose location is defined relative to a reference point within the data structure in which the operand appears.

Figure 2.14 A list of students' marks.

Several variations of basic form provide for very efficient access to memory operands in practical programming situations. For Example,

(Ri Rj)

The effective address is the sum of the contents of registers Ri and Rj. The second register is usually called the base register.

Figure 2.15 Indexed addressing used in accessing test scores in the list in Figure 2.14.

#### **RELATIVE ADDRESSING:**

Then, X(PC) can be used to address a memory location that is X bytes away from the location presently pointed to by the program counter. Since the addressed location is identified "relative" to the program counter, which always identifies the current execution point in a program, the name Relative mode is associated with this type of addressing.

Relative mode: The effective address is determined by the Index mode using the program counter in place of the general-purpose register Ri.

This mode can be used to access data operands. But, it's most common use is to specify the target address in branch instructions. An instruction such as

Branch>0 LOOP

causes program execution to go to the branch target location identified by the name LOOP if the branch condition is satisfied.

#### **APDITIONAL MODES:**

Autoincrement mode: The effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are automatically incremented to point to the next item in a list.

Autoincrement mode can be denoted by putting the specified register in parentheses, to show that the contents of the register are used as the effective address, followed by a plus sign to indicate that these contents are to be incremented after the operand is accessed. Thus, the Autoincrement mode is written as

(Ri)+

Implicitly, the increment amount is 1 when the mode is given in this form.

Autodecrement mode: The contents of a register specified in the instruction are first automatically decremented and are then used as the effective address of the operand.

Autodecrement mode can be denoted by putting the specified register in parentheses, preceded by a minus sign to indicate that the contents of the register are to be decremented before being used as the effective address. Thus, we write

-(Ri)

Figure 2.16 The Autoincrement addressing mode used in the program of Figure 2.12.

In this mode, operands are accessed in descending address order.

# Basic input/output operations

We now examine the means by which data are transferred between the memory of a computer and the outside world. Input/Output (I/O) operations are essential, and the way they are performed can have a significant effect on the performance of the computer.

Consider a task that reads in character input from a keyboard and produces character output on a display screen. A simple way of performing such I/O tasks is to use a method known as program- controlled I/O. The rate of data transfer from the keyboard to a computer is limited by the typing speed of the user, which is unlikely to exceed a few characters per second. The rate of output transfers from the computer to the display is much higher. It is determined by the rate at which characters can be transmitted over the link between the computer and the display device, typically several thousand characters per second. However, this is still much slower than the speed of a processor that can execute many millions of instructions per second. The difference in speed between the processor and I/O devices creates the need for mechanisms to synchronize the transfer of data between them.

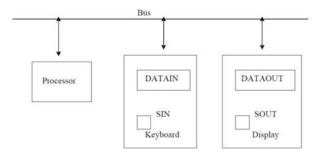

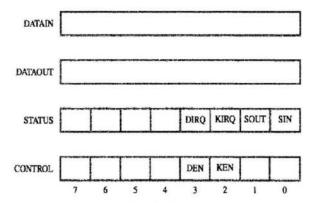

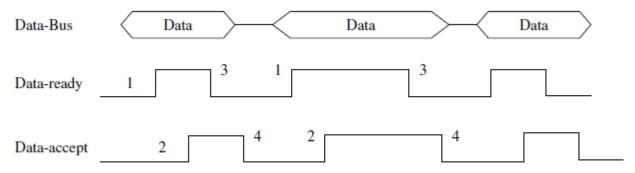

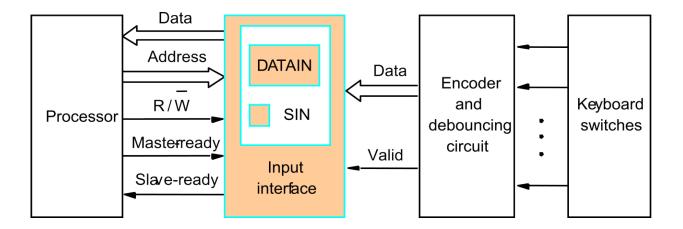

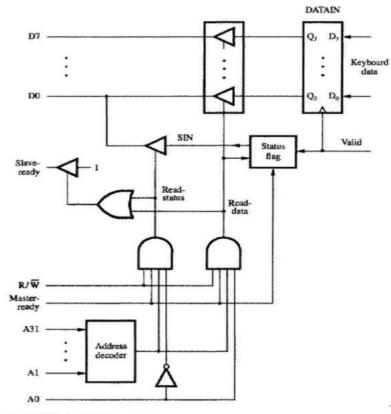

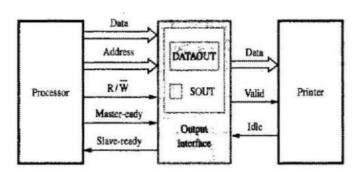

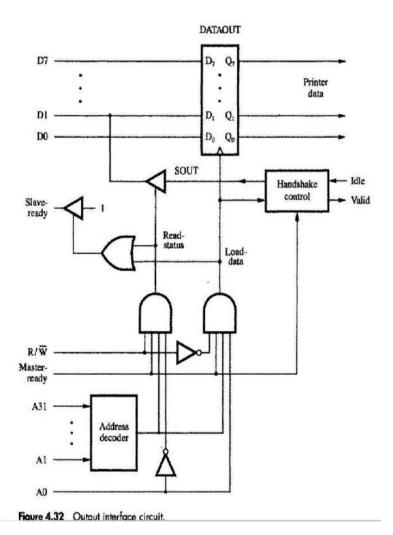

Fig a Bus connection for processor, keyboard, and display

The keyboard and the display are separate device as shown in fig a. the action of striking a key on the keyboard does not automatically cause the corresponding character to be displayed on the screen. One block of instructions in the I/O program transfers the character into the processor, and another associated block of instructions causes the character to be displayed.

Striking a key store the corresponding character code in an 8-bit buffer register associated with the keyboard. Let us call this register DATAIN, as shown in fig a. To inform the processor that a valid character is in DATAIN, a status

control flag, SIN, is set to 1. A program monitors SIN, and when SIN is set to 1, the processor reads the contents of DATAIN. When the character is transferred to the processor, SIN is automatically cleared to 0. If a second character is entered at the keyboard, SIN is again set to 1, and the processor repeats.

An analogous process takes place when characters are transferred from the processor to the display. A buffer register, DATAOUT, and a status control flag, SOUT, are used for this transfer. When SOUT equals 1, the display is ready to receive a character.

In order to perform I/O transfers, we need machine instructions that can check the state of the status flags and transfer data between the processor and the I/O device. These instructions are similar in format to those used for moving data between the processor and the memory. For example, the processor can monitor the keyboard status flag SIN and transfer a character from DATAIN to register R1 by the following sequence of operations.

# Stacks and queues

A computer program often needs to perform a particular subtask using the familiar subroutine structure. In order to organize the control and information linkage between the main program and the subroutine, a data structure called a stack is used. This section will describe stacks, as well as a closely related data structure called a queue.

Data operated on by a program can be organized in a variety of ways. We have already encountered data structured as lists. Now, we consider an important data structure known as a stack. A stack is a list of data elements, usually words or bytes, with the accessing restriction that elements can be added or removed at one end of the list only. This end is called the top of the stack, and the other end is called the bottom. Another descriptive phrase, last-in-first-out (LIFO) stack, is also used to describe this type of storage mechanism; the last data item placed on the

stack is the first one removed when retrieval begins. The terms push and pop are used to describe placing a new item on the stack and removing the top item from the stack, respectively.

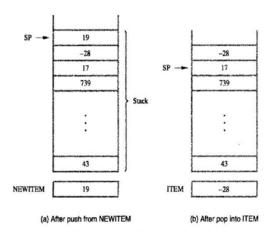

Fig b shows a stack of word data items in the memory of a computer. It contains numerical values, with 43 at the bottom and -28 at the top. A processor register is used to keep track of the address of the element of the stack that is at the top at any given time. This register is called the stack pointer (SP). It could be one of the general-purpose registers or a register dedicated to this function.

Figure 2.22 Effect of stack operations on the stack in Figure 2.21.

Department of CSE, AITS-TIRUPATI

Another useful data structure that is similar to the stack is called a queue. Data are stored in and retrieved from a queue on a first-in-first-out (FIFO) basis. Thus, if we assume that the queue grows in the direction of increasing addresses in the memory, which is a common practice, new data are added at the back (high-address end) and retrieved from the front (low-address end) of the queue.

There are two important differences between how a stack and a queue are implemented. One end of the stack is fixed (the bottom), while the other end rises and falls as data are pushed and popped. A single pointer is needed to point to the top of the stack at any given time. On the other hand, both ends of a queue move to higher addresses as data are added at the back and removed from the front. So, two pointers are needed to keep track of the two ends of the queue.

Another difference between a stack and a queue is that, without further control, a queue would continuously move through the memory of a computer in the direction of higher addresses. One way to limit the queue to a fixed region in memory is to use a circular buffer. Let us assume that memory addresses from BEGINNING to END are assigned to the queue. The first entry in the queue is entered into location BEGINNING, and successive entries are appended to the queue by entering them at successively higher addresses. By the time the back of the queue reaches END, space will have been created at the beginning if some items have been removed from the queue. Hence, the back pointer is reset to the value BEGINNING and the process continues. As in the case of a stack, care must be taken to detect when the region assigned to the data structure is either completely full or completely empty.

#### **Subroutines**

In a given program, it is often necessary to perform a particular subtask many times on different data-values. Such a subtask is usually called a subroutine. For example, a subroutine may evaluate the sine function or sort a list of values into increasing or decreasing order.

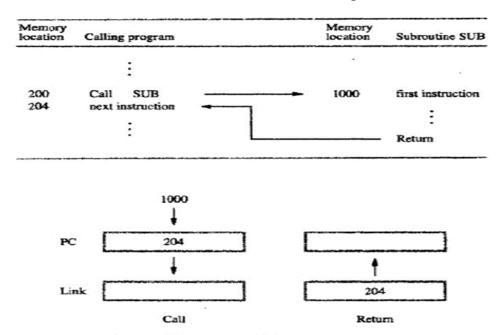

It is possible to include the block of instructions that constitute a subroutine at every place where it is needed in the program. However, to save space, only one copy of the instructions that constitute the subroutine is placed in the memory, and any program that requires the use of the subroutine simply branches to its starting location. When a program branches to a subroutine we say that it is calling the subroutine. The instruction that performs this branch operation is named a Call instruction.

After a subroutine has been executed, the calling program must resume execution, continuing immediately after the instruction that called the subroutine. The subroutine is said to return to the program that called it by executing a Return instruction.

The way in which a computer makes it possible to call and return from subroutines is referred to as its subroutine linkage method. The simplest subroutine linkage method is to save the return address in a specific location, which may be a register dedicated to this function. Such a register is called the link register. When the subroutine completes its task, the Return instruction returns to the calling program by branching indirectly through the link register.

The Call instruction is just a special branch instruction that performs the following operations

Store the contents of the PC in the link register

Branch to the target address specified by the instruction.

The Return instruction is a special branch instruction that performs the operation.

Branch to the address contained in the link register.

Figure 2.24 Subroutine linkage using a link register.

#### SUBROUTINE NESTING AND THE PROCESSOR STACK:-

A common programming practice, called subroutine nesting, is to have one subroutine call another. In this case, the return address of the second call is also stored in the link register, destroying its previous contents. Hence, it is essential to save the contents of the link register in some other location before calling another subroutine. Otherwise, the return address of the first subroutine will be lost.

Subroutine nesting can be carried out to any depth. Eventually, the last subroutine called completes its computations and returns to the subroutine that called it. The return address needed for this first return is the last one generated in the nested call sequence. That is, return addresses

are generated and used in a last-in-first-out order. This suggests that the return addresses associated with subroutine calls should be pushed onto a stack. A particular register is designated as the stack pointer, SP, to be used in this operation. The stack pointer points to a stack called the processor stack. The Call instruction pushes the contents of the PC onto the processor stack and loads the subroutine address into the PC. The Return instruction pops the return address from the processor stack into the PC.

## Logic instructions

Logic operations such as AND, OR, and NOT, applied to individual bits, are the basic building blocks of digital circuits, as described. It is also useful to be able to perform logic operations is software, which is done using instructions that apply these operations to all bits of a word or byte independently and in parallel. For example, the instruction

Not dst

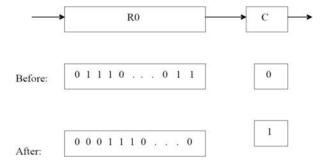

#### SHIFT AND ROTATE INSTRUCTIONS:-

There are many applications that require the bits of an operand to be shifted right or left some specified number of bit positions. The details of how the shifts are performed depend on whether the operand is a signed number or some more general binary-coded information. For general operands, we use a logical shift. For a number, we use an arithmetic shift, which preserves the sign of the number.

# Logical shifts:-

Two logical shift instructions are needed, one for shifting left (LShiftL) and another for shifting right (LShiftR). These instructions shift an operand over a number of bit positions specified in a count operand contained in the instruction. The general form of a logical left shift instruction is

# LShiftL count, dst

# Logical shift left LShiftL #2, R0

# (b) Logical shift right LShiftR #2, R0

# (c) Arithmetic shift right AShiftR #2, R0

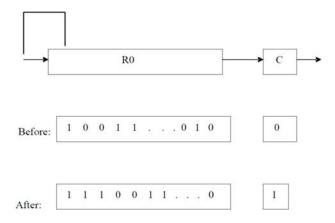

# **Rotate Operations:-**

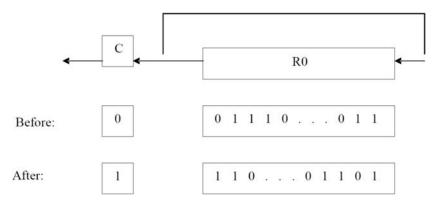

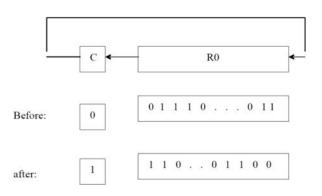

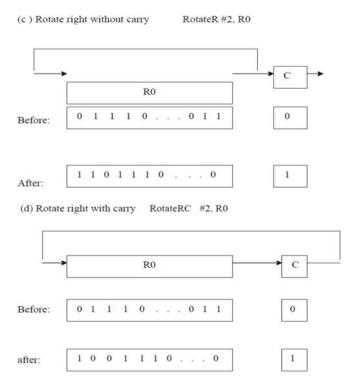

In the shift operations, the bits shifted out of the operand are lost, except for the last bit shifted out which is retained in the Carry flag C. To preserve all bits, a set of rotate instructions can be used. They move the bits that are shifted out of one end of the operand back into the other end. Two versions of both the left and right rotate instructions are usually provided. In one version, the bits of the operand are simply rotated. In the other version, the rotation includes the C flag.

# (a) Rotate left without carry RotateL #2, R0

# (b) Rotate left with carry RotateLC #2, R0

#### MULTIPLICATION AND DIVISION

'Two signed integers can be multiplied or divided by machine instructions with the same format. The instruction

Multiply Ri, Rj

performs the operation

$$Rj \leftarrow [Ri] \times [Rj]$$

The product of two n-bit numbers can be as large as 2n bits. A number of instruction sets have a Multiply instruction that computes the lew-order n bits of the product and places i in register Rj, as indicated. To accommodate the general 2n-bit product case, some processors produce the product in two registers, usually adjacent registers Rj and R(j + 1), with the high-order half being placed in register R(j + 1).

Some instruction sets provide a signed integer Divide instruction

Divide Ri,Rj

which performs the operation

$$Rj \leftarrow [Rj]/[Ri]$$

placing the quotient in Rj. The remainder may be placed in R(j + 1), or it may be Lost.

#### **UNIT-II**

Arithmetic: Addition and Subtraction of Signed Numbers, Design and Fast Adders, Multiplication of Positive Numbers, Signed-operand Multiplication, Fast Multiplication, Integer Division, Floating-Point Numbers and Operations.

Basic Processing Unit: Fundamental Concepts, Execution of a Complete Instruction, Multiple-Bus Organization, Hardwired Control, Multiprogrammed Control.

#### CHAPTER-1

#### Arithmetic

#### 2.1 ADDITION AND SUBTRACTION OF SIGNED NUMBERS

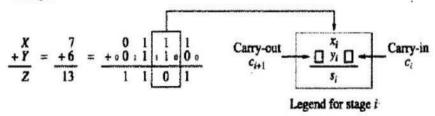

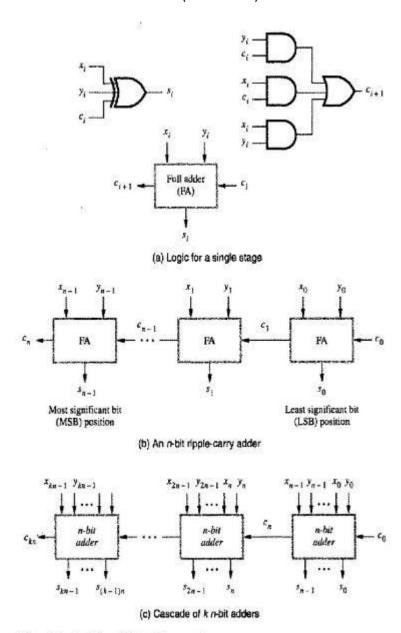

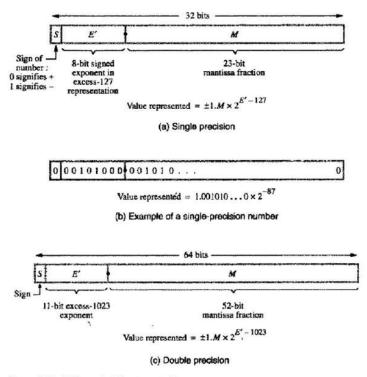

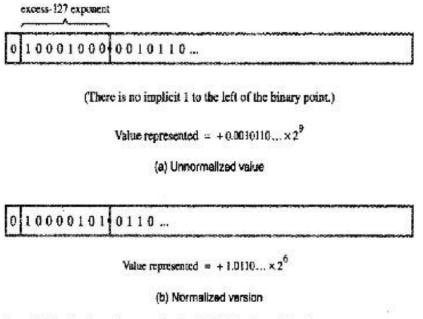

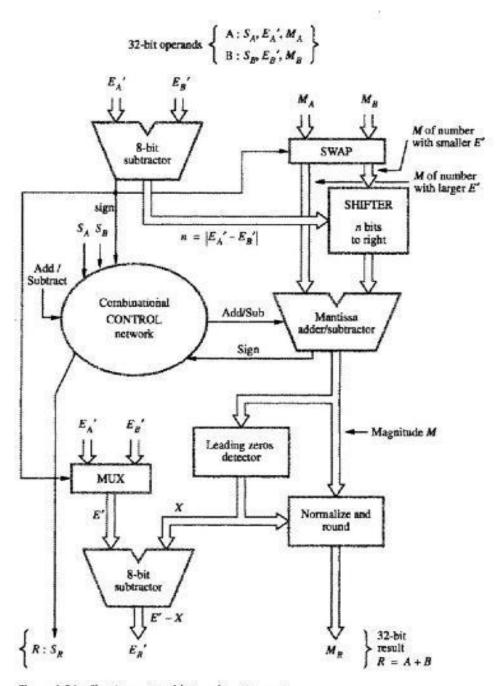

Figure 6.1 shows the logic truth table for the sum and carry-out functions for adding equally weighted bits x; and y, in two numbers X and Y, The figure also shows logic expressions for these functions, along with an example of addition of the 4-bit unsigned numbers 7 and 6. Note that each stage of the addition process must accommodate a carry-in bit. We use C to represent the carry-in to the I stage, which is the same as the carry-out from the I stage.

The logic expression for si in Figure 6.1 can be implemented with a 3-input XOR gate, used in Figure 6.2a as part of the logic required for a single stage of binary addition. The carry-out function, ci+1, is implemented with a two-level AND-OR logic circuit. A convenient symbol for the complete circuit for a single stage of addition, called a full adder (FA), is also shown in the figure.

A cascaded connection of such n full adder blocks, as shown in Figure 6.2C, forms a parallel adder & can be used to add two n-bit numbers. Since the carries must propagate, or ripple, through this cascade, the configuration is called an n-bit ripple-carry adder.

The carry-in,  $C_0$ , into the *least-significant-bit (LSB)* position [1<sup>st</sup> stage] provides a convenient means of adding 1 to a number. Take for instance; forming the 2's- complement of a number involves adding 1 to the 1's-complement of the number. The carry signals are also useful for interconnecting k adders to form an adder capable of handling input numbers that are **kn** bits long, as shown in Figure 6.2c.

| $x_i$ | $y_i$ | Carry-in ci | Sum si | Carry-out $c_{i+1}$ |

|-------|-------|-------------|--------|---------------------|

| 0     | 0     | 0 [         | 0      | 0                   |

| 0     | 0     | 1 1         | 1      | 0                   |

| 0     | i     | 0           | 1      | 0                   |

| 0     | . 1   | 1           | 0      | 1                   |

| 1     | 0     | 0           | 1      | 0                   |

| 1     | 0     | 1           | 0      | 1                   |

| 1     | 1     | 0           | 0      | 1                   |

| 1     | i     | 1           | 1      | i                   |

$$\begin{aligned} s_i &= \overline{x_i} \overline{y_i} c_i + \overline{x_i} y_i \overline{c_i} + x_i \overline{y_i} \overline{c_i} + x_i y_i c_i = x_i \oplus y_i \oplus c_i \\ c_{i+1} &= y_i c_i + x_i c_i + x_i y_i \end{aligned}$$

Example:

Figure 6.1 Logic specification for a stage of binary addition.

Figure 6.2 Logic for addition of binary vectors.

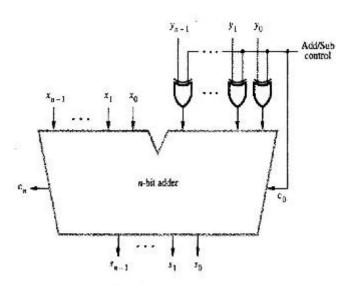

# ADDITION/SUBTRACTION Logic UNIT:

The n-bit adder in Figure 6.28 can be used to add 2's-complement numbers X and Y, where the Xn-1 and yn-1 bits are the sign bits. Overflow can only occur when the signs of the two operands are the same. In this case, overflow obviously occurs if the sign of the result is different, therefore, a circuit to detect overflow can be added to the n-bit adder by implementing the logic expression

$$s_i = \overline{x_i} \overline{y_i} c_i + \overline{x_i} y_i \overline{c_i} + x_i \overline{y_i} \overline{c_i} + x_i y_i c_i = x_i \oplus y_i \oplus c_i$$

$$c_{i+1} = y_i c_i + x_i c_i + x_i y_i$$

Overflow can also occur when the carry bits c, and  $c_{n-1}$  are different. Therefore, a simpler alternative circuit for detecting overflow can be obtained by implementing the expression **cn**  $\square$  **cn-1** with an XOR gate.

In order to perform the subtraction operation X - Y on 2's-complement numbers X and Y, we form the 2's-complement of Y and add it to X. The logic circuit network shown in Figure 6.3 canbe used to perform either addition or subtraction based on the value applied to the Add/Sub input control line. This line is set to 0 for addition, applying the Y vector unchanged to one of the adder inputs along with a carry-in signal, co, of 0, When the Add/Sub control line is set to 1, the Y vector is 1's-complemented (that is, bit complemented) by the XOR gates and co is set to 1 to complete the 2's-complementation of Y. An XOR gate can be added to Figure 6.3 to detect the overflow condition **cn**  $\square$  **cn-1**.

Figure 6.3 Binary addition-subtraction logic network.

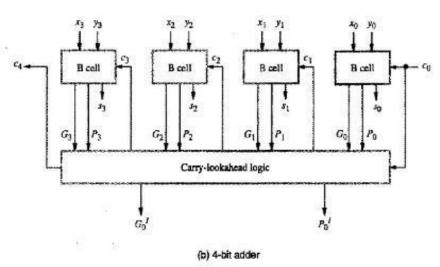

### **DESIGN OF FAST ADDERS:**

In an n-bit parallel adder (ripple-carry adder), there is too much delay in developing the outputs, so through sn-1 and cn. On many occasions this delay is not acceptable; in comparison with the speed of other processor components and speed of the data transfer between registers and cache memories. The delay through a network depends on the integrated circuit technology used in fabricating the network and on the number of gates in the paths from inputs to outputs (propagation delay). The delay through any combinational logic network constructed from gates in a particular technology is determined by adding up the number of logic-gate delays along the longest signal propagation path through the network. In the case of the n-bit ripple-carry adder, the longest path is from inputs x0, y0, and c0 at the least-significant-bit (LSB) position to outputs cn and sn-1 at the most-significant-bit (MSB) position.

Using the logic implementation indicated in Figure 6.2a,  $c_{n-1}$  is available in 2(n-1) gate delays, and  $s_{n-1}$  is one XOR gate delay later. The final carry-out,  $c_{n}$  is available after 2n gate delays. Therefore, if a ripple-carry adder is used to implement the addition/subtraction unit shown in Figure-6.3, all sum bits are available in 2n gate delays, including the delay through the XOR

gates on the Y input. Using the implementation  $\mathbf{cn} \ \square \ \mathbf{cn-1}$  for overflow, this indicator is available after 2n+2 gate delays. In summary, in a parallel adder an nth stage adder cannot complete the addition process before all its previous stages have completed the addition even with input bits ready. This is because; the carry bit from previous stage has to be made available for addition of the present stage.

In practice, a number of design techniques have been used to implement high- speed adders. In order to reduce this delay in adders, an augmented logic gate network structure may be used. One such method is to use circuit designs for fast propagation of carry signals (carry prediction).

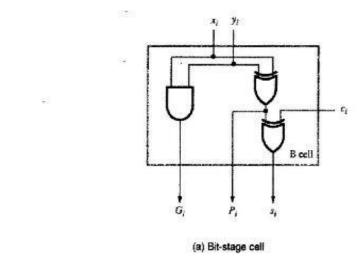

## Carry-Look ahead Addition:

As it is clear from the previous discussion that a parallel adder is considerably slow & a fast adder circuit must speed up the generation of the carry signals, it is necessary to make the carry input to each stage readily available along with the input bits.

This can be achieved either by propagating the previous carry or by generating a carry depending the input bits & previous carry. The logic expressions for si (sum) and ci+1 (carry-out) of stagei are

$$s_i=x_i\oplus y_i\oplus c_i$$

and

$$c_{i+1}=x_iy_i+x_ic_i+y_ic_i$$

Factoring the second equation into

$$c_{i+1}=x_iy_i+(x_i+y_i)c_i$$

we can write

$$c_{i+1}=G_i+P_ic_i$$

where

$$G_i=x_iy_i \quad \text{and} \quad P_i=x_i+y_i$$

The expressions  $G_i$  and  $P_i$  are called *generate* and *propagate* functions for stage i. If the generate function for stage i is equal to 1, then  $c_i+1=1$ , independent of the input carry,  $c_i$ . This occurs when both  $x_i$  and  $y_i$  are 1. The propagate function means that an input carry will produce an output carry when either  $x_i$  or  $y_i$  or both equal to 1. Now, using  $G_i$  &  $P_i$  functions we can decide carry for  $i^{th}$  stage even before its previous stages have completed their addition operations. All  $G_i$  and  $P_i$  functions can be formed independently and in parallel in only one gate delay after the  $X_i$  and  $Y_i$  inputs are applied to an n-bit adder. Each bit stage contains an AND gate to form  $G_i$ , an OR gate to form  $P_i$  and a three-input XOR gate to form  $S_i$ . However, a much simpler circuit can be derived by considering the propagate function as  $P_i = x_i$   $P_i$   $P_i$  P

Consider the ci+1 expression

$$c_{i+1} = C_i + P_i C_{i-1} + P_i P_{i-1} c_{i-1}$$

This is because, Ci = (Gi-1 + Pi-1Ci-1).

Further,  $C_{i-1} = (G_{i-2} + P_{i-2}C_{i-2})$  and so on. Expanding in this fashion, the final carry expression can be written as below;

$$c_{i+1} = G_i + P_i G_{i-1} + P_i P_{i-1} G_{i-2} + \cdots + P_i P_{i-1} \cdots P_1 G_0 + P_i P_{i-1} \cdots P_0 c_0$$

Thus, all carries can be obtained in three gate delays after the input signals Xi, Yi and Cin are applied at the inputs. This is because only one gate delay is needed to develop all Pi and Gi signals, followed by two gate delays in the AND-OR circuit (SOP expression) for ci after a further XOR gate delay, all sum bits are available. Therefore, independent of n, the number of stages, the n-bit addition process requires only four gate delays.

Figure 6.4 4-bit carry-lookahead adder.

Now, consider the design of a 4-bit parallel adder. The carries can be implemented as

$$c_3 = G_0 + P_0 c_0$$

$$c_2 = G_1 + P_1 G_0 + P_1 P_0 c_0$$

$$c_3 = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 c_0$$

$$c_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 c_0$$

The complete 4-bit adder is shown in Figure 6.4b where the B cell indicates Gi, Pi & Sigenerator. The carries are implemented in the block labeled carry look-ahead logic. An adder implemented in this form is called a carry look ahead adder. Delay through the adder is 3 gate delays for all carry bits and 4 gate delays for all sum bits. In comparison, note that a 4-bit ripple- carry adder requires 7 gate delays for S3(2n-1) and 8 gate delays(2n) for c4.

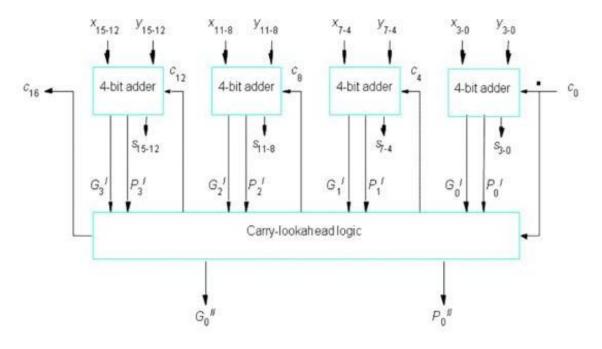

If we try to extend the carry lookahead adder of Figure 5b for longer operands, we run into a problem of gate fan-in constraints. From the final expression for Ci+1 & the carry expressions for a 4 bit adder, we see that the last AND gate and the OR gate require a fan-in of i + 2 in generating cn-1. For c4 (i = 3)in the 4-bit adder, a fan-in of 5 is required. This puts the limit on the practical implementation. So the adder design shown in Figure 4b cannot be directly extended to longer operand sizes. However, if we cascade a number of 4-bit adders, it is possible to build longer adders without the practical problems of fan- in. An example of a 16 bit carry look ahead adder is as shown in figure. Eight 4-bit carry look-ahead adders can be connected asin Figure-6.2 to form a 32-bit adder.

FIG: 16 bit carry-lookahead adder

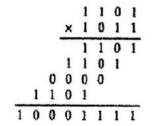

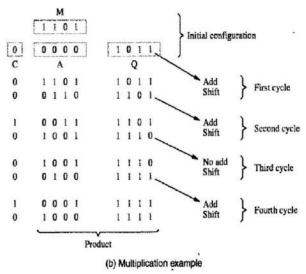

### MULTIPLICATION OF POSITIVE NUMBERS

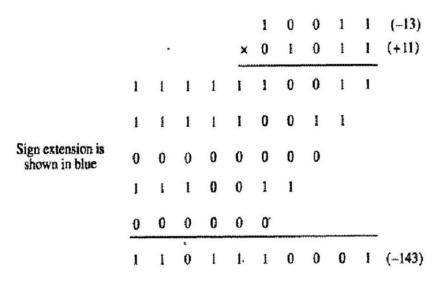

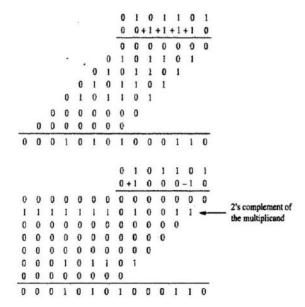

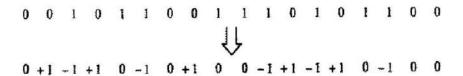

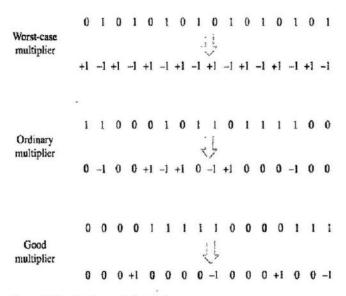

Consider the multiplication of two integers as in Figure-6a in binary number system. This algorithm applies to unsigned numbers and to positive signed numbers. The product of two n- digit numbers can be accommodated in 2n digits, so the product of the two 4-bit numbers in this example fits into 8 bits. In the binary system, multiplication by the multiplier bit '1' means the multiplicand is entered in the appropriate position to be added to the partial product. If the multiplier bit is '0', then 0s are entered, as indicated in the third row of the shown example.

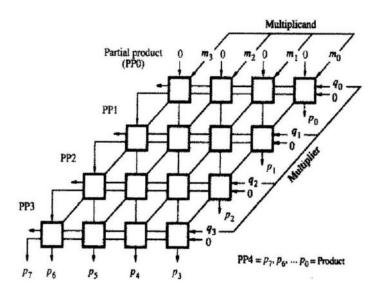

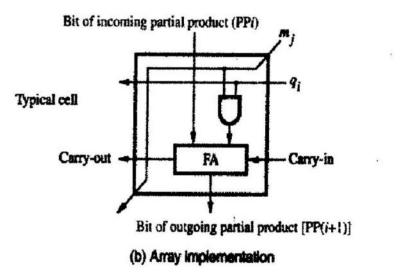

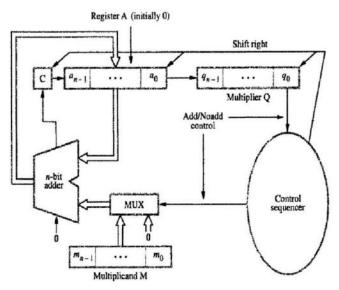

Binary multiplication of positive operands can be implemented in a combinational (speed up) two-dimensional logic array, as shown in Figure 6.6. Here, M- indicates multiplicand, Q- indicates multiplier & P- indicates partial product. The basic component in each cell is a full adder FA. The AND gate in each cell determines whether a multiplicand bit mj, is added to the incoming partial-product bit, based on the value of the multiplier bit, qi. For i in the range of 0 to 3, if qi = 1, add the multiplicand (appropriately shifted) to the incoming partial product, PPi, to generate the outgoing partial product, PP(i+ 1) & if qi = 0, PPi is passed vertically downward unchanged. The initial partial product PPO is all 0s. PP4 is the desired product. The multiplicand is shifted left one position per row by the diagonal signal path. Since the multiplicand is shifted and added to the partial product depending on the multiplier bit, the method is referred as SHIFT & ADD method. The multiplier array & the components of each bit cell are indicated in the diagram, while the flow diagram shown explains the multiplication procedure.

(13) Multiplicand M

(11) Multiplier Q

(143) Product P

(a) Manual multiplication algorithm

Fig 6.6: Array multiplication of positive binary operands

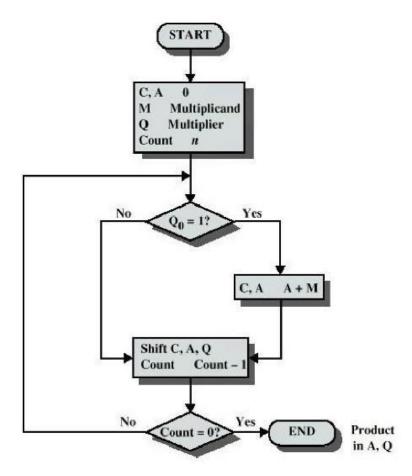

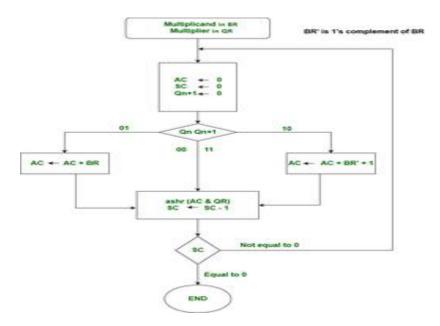

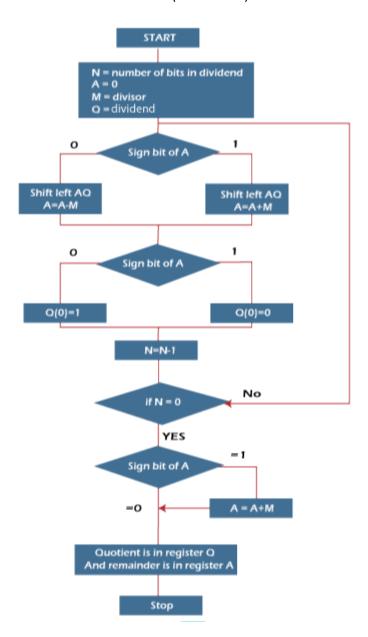

The following SHIFT & ADD method flow chart depicts the multiplication logic for unsignednumbers.

Despite the use of a combinational network, there is a considerable amount of delay associated with the arrangement Department of CSE,AITS-TIRUPATI 42

shown. Although the preceding combinational multiplier is easy to

understand, it uses many gates for multiplying numbers of practical size, such as 32- or 64-bit numbers. The worst case signal propagation delay path is from the upper right corner of the arrayto the high-order product bit output at the bottom left corner of the array. The path includes the two cells at the right end of each row, followed by all the cells in the bottom row. Assuming that there are two gate delays from the inputs to the outputs of a full adder block, the path has a total of 6(n - 1) - 1 gate delays, including the initial AND gate delay in all cells, for the n x n array. In the delay expression, (n-1) because, only the AND gates are actually needed in the first row of the array because the incoming (initial) partial product PPO is zero

Multiplication can also be performed using a mixture of combinational array techniques (similar to those shown in Figure 7) and sequential techniques requiring less combinational logic. Multiplication is usually provided as an instruction in the machine instruction set of a processor. High-performance processor (DS processors) chips use an appreciable area of the chip to perform arithmetic functions on both integer and floating-point operands. Sacrificing an area on- chip for these arithmetic circuits increases the speed of processing. Generally, processors built for real time applications have an on-chip multiplier.

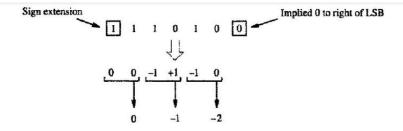

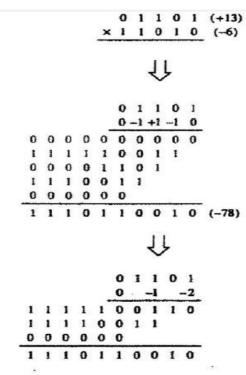

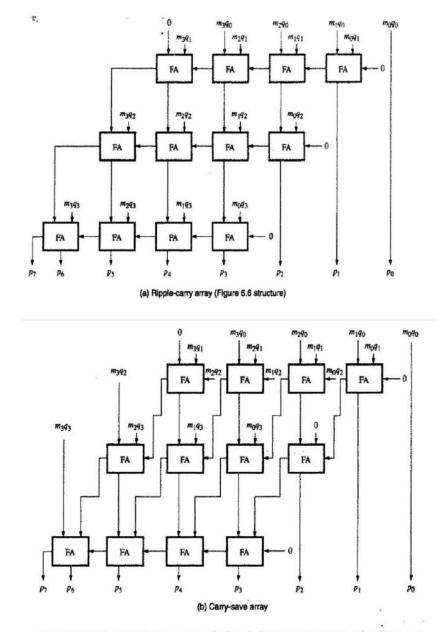

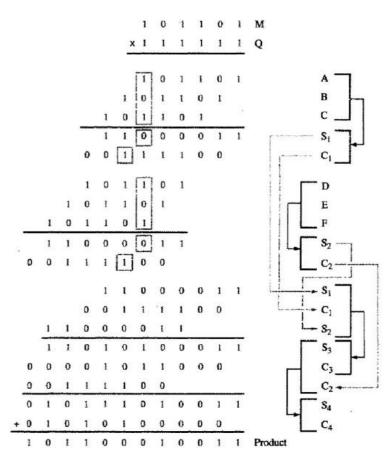

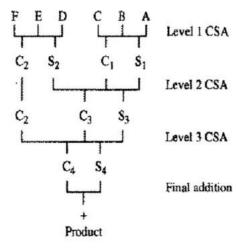

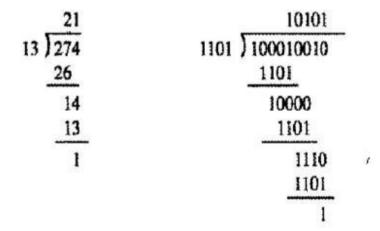

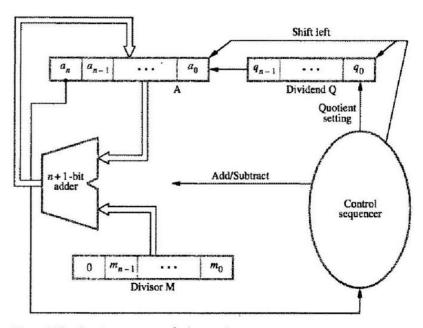

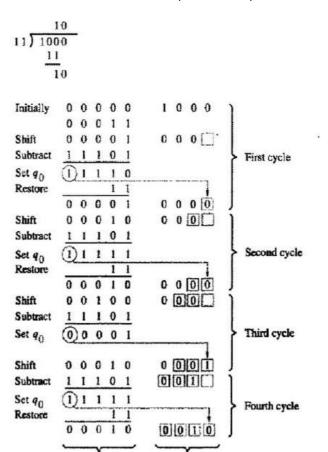

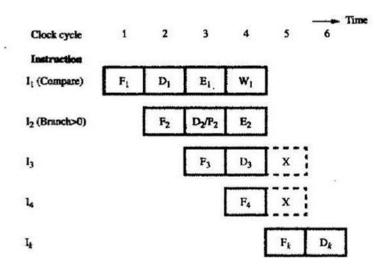

(a) Register configuration