# ANNAMACHARYA INSTITUTE OF TECHNOLOGY AND SCIENCES

(Autonomous)

Approved by AICTE, New Delhi & Permanent Affiliation to JNTUA, Anantapur.

Three B. Tech Programmes (CSE, ECE & CE) are accredited by NBA, New Delhi, Accredited by NAAC with 'A' Grade, Bangalore.

A-grade awarded by AP Knowledge Mission. Recognized under sections 2(f) & 12(B) of UGC Act 1956.

Venkatapuram Village, Renigunta Mandal, Tirupati, Andhra Pradesh-517520.

#### **Department of Computer Science and Engineering**

#### Academic Year 2023-24

II. B.Tech I Semster

# Digital Electronics & Microprocessors (20APC0503/ 20APC3601)

**Prepared By**

Ms. Deveswari Assistant Professor Department of ECE, AITS

## Number System:

Number system is a basis for counting various items. On hearing the word 'number, all of us immediately think of the familiar decimal number system with its 10 digits; 0,1,2,3,4,5,6,7,8 and 9.

Modern computers communicate and operate with binary numbers which use only the digits of end 1. For large clecimal quantities are cleal with very large binary strings and therefore they do not like working with binary numbers. This gave rise to three new number systems.

- · Octal > 3 + OLVE + DIXO I DIXO + DIXE + DIXE

- · Hexardecimal

- · Binary Coded Decimal (BCD)

- → To define any number system, we have to specify following aspects:

- \* Base of the number system such as 2,8,10 or 16.

- \* The base (01) Madine decides the total number of digits available in that number system.

- \* First digit in the number system is always zero (0) and last digit in the number system is always.

- \* In general a number in a system having base can be written as

anxon+an-1xon-1+---+aoxon+a-1xon+a-2xon2+----+a-mxonim

Where anz the value of the nth digit, on= madix.

Decimal Number System:

The decimal number system contain ten unique symbols 0,1,2,3,4,5,6,7,8 and 9.

In decimal system 10 symbols are involved, so the base or radix

. It is a weighted number system.

The value attached to the symbol depends on its

In general, dn dn-1 dn-2: -- dn·d-1 d-2 --- d-m

is given by

(dn×10<sup>n</sup>) + (dn+×10<sup>n-1</sup>) + --- + (do×10°) + (d-1×10<sup>-1</sup>)

= 9x1000 + 2x10 + 6x10 + 6x10 + 6x10 + 6x10 2 = 9x1000 + 2x100 + 5x10 + 6 + (2/10) + (6/100).

Binary Number System:

- The binary number system is a weighted system

- · The base of this number system is 2.

- . It has two independent symbols

- . The symbols used are o and 1.

- · A binary digit in called a bit.

E21- 1101.101

=>  $1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{2} + 1 + 1 \times 2^{2} + 0 \times 2^{2} + 1 \times 2^{3}$ => 8 + 4 + 0 + 1 + 0.5 + 0 + 0.125=>  $(13 - 625)_{10}$

# Octol Number System

- · It is also a weighted system.

- . Its bone on modine is 8

- · It has 8 independent symbols 0,1,2,3,4,5,6 and 7.

- Its base  $8 = 2^3$ , every 3-bit group of binary can be separemented by an octal digit.

Exi- (587)8 000 CAON

### Hexa Decimal Number System!

- . The hexadecimal number system is a weighted system.

- . The base on sadise of their number system is 16.

- · The symbols used are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and

- The base 16 = 24, every 4-bit group of binary can be represented by an hexadecimal oligit.

Ex!- (3FD) 16. 81.0 82810

### Conversions

· Decimal to binary Conversion:

in Convert (52) 10 into binary

Soll-

$$2 | 52$$

$2 | 26 - 0$

$2 | 13 - 0$

$2 | 3 - 0$

$1 - 1$

(11) Convert (105.15)10 into binary

Integen part Fraction part

0.80 × 2 = 1.60 ->

maly strategies

(105.15)10 = (1101001:001001)2

. Decimal to octal Conversion:

in Convert (378.93)10 into octal.

$$8 \boxed{378}$$

$$8 \boxed{47} - 2$$

$$0.93 \times 8 = 7.44 \rightarrow 7$$

$$0.44 \times 8 = 3.52 \rightarrow 3$$

$$0.59 \times 8 = 0.16$$

to to be a superior of the mission of the

(378.93)10 = (572.7341)8

. Decimal to hexadecimal convention: of the convention · Convert (2598.675)10 into hexadecimal.

(2598.675)10 = (A26.ACCC)16

```

3

and the second of the second

1015

```

010

Binary to Decimal Conversion 1) Convert (10101)2 to decimal

$$(10101)_{2} = (1x2^{4}) + (0x2^{3}) + (1x2^{2}) + (0x2^{1}) + (1x2^{0})$$

$$= 16 + 0 + 4 + 0 + 1$$

$$= (21)_{10}$$

iii, Convert (111.101)2 to decimal

$$(111\cdot101)_{2} = (1\times2^{2}) + (1\times2^{1}) + (1\times2^{0}) + (1\times2^{-1}) + (0\times2^{-2}) + (1\times2^{-3})$$

$$= 4+2+1+0.5+0+0.125$$

$$= 7.625$$

Octal to Decimal Conversion 1 0101011101

Convert (756.603)8 to decimal

$$(756.603)_8 = (7x8^2) + (5x8') + (6x8^0) + (6x8^1) + (0x8^2) + (3x8^3)$$

= 448 +40+6+0-75+0+0.005 delse ola (mo 100 moron) | wis

Hexadecimal to decimal conversion

Convert (AOF9.0EB)16 to decimal

$$(AOF9.0EB)_{16} = (10 \times 16^{3}) + (0 \times 16^{2}) + (15 \times 16^{1}) + (9 \times 16^{6}) + (0 \times 16^{-1}) + (14 \times 16^{-2}) + (11 \times 16^{-3})$$

= 40960+0+240+9+0+0.0546+0.0026

Binary to octal Conversion

for binary to octal conversion the binary numbers are divided into groups of 3 bits each.

| etal | binaxy | 4101010101                                |

|------|--------|-------------------------------------------|

| 0    | 000    | 01(10)                                    |

| 1    | 001    |                                           |

| 2    | 010    | Convert (111-101)x to decimal             |

| 3    | 011    | ) + (*em) + (*em) + (*em) + (*em) + (*em) |

| 5    | 101    | 2 CHO 4 O + C O + H + C + H > C           |

| 6    | 110    |                                           |

| 7    | 11.1   | 000.4 #                                   |

in Convent (10111010110.110110011)2 into octal.

5 7 2 6 10 60 6 3 a(800-88F) trovoo

0, (51.404) =

(ioniloioilo·110110011)2 = (5+26.663)8

in Convert (10101111001-0111)2 into octal.

2 5 7 1 3 4 of all (A) PHOAD TO STORY OF STORY

→ (10101111001:0111)2 = (2571·34)8

er(spectores) =

# Binary to Hexadecimal conversion:

too binary to hexaelecimal conversion the binary numbers are divided into groups of 4 bits each.

| navy |

|------|

| 000  |

| 001  |

| 010  |

| ),11 |

| 00   |

| 01   |

| 10   |

| 11   |

|      |

in Convert (1011011011) 2 into hexadecimal

00101101101101 0111 1001 0101 1100

Conocacho, puisocolomos) = Mas colomos

⇒ (1011011011)<sub>2</sub> = (20B)<sub>16</sub>

ii, Convert (01011111011.011111)2 into hexadecimal.

2 F B . 7 C

> (01011111011.011111) = (2FB.7C)16

Octal to Binary Conversion:

were the front with the first of To Convert octal number to binary, replace each octal digit by its 3-bit binary equivalent.

Convert (367-52)8 into birary

367.52

011 110 111 101 010

=> (367.52)8 = (011110111.101010)2

Hexadecimal to Binary Conversion:

To Convert Horadecimal number to binary, neplace each hexadecimal digit by its 4-bit binary group. Convert (3A9E-BOD) into binary

(3A9 6 . BOD) 16 0 0 0 (1101101101) 100000

0011 1010 1001 1110 1011 0000 1101

=> (3A9E · BOD)16 = (00111010101010110 · 101100001101)2

Octal to hexadecimal conversion: (1101101101)

for octal to Hexadecimal conversion, first convert the given octal numbers to binary and then binary number to hexadecimal.

Convert (756.603), to hexadecimal

7 5 6. 603 111 101 110 110 000 BH

0001 1110 1110 · 1100 0001 1000

=> (756.603)8 = (1EE.C18)16

Hexadecimal to Octal Conversion

For hexadecimal to octal Conversion, first convert the given hexadecimal number to binary and then binary number to octal.

Convert (B9FAE), to Octal

1011 1001 1111 · 1010 · 1110

5 6 3 7 . 5 3 4

=> (B9F.AE)16 = (5637.534)8

### Binary Arithematic Operation:

1. Birary Addition:

0+0 =0, 0+1 =1, 1+0 =1, 1+1 = 10, i.e. 0 with carry 1

\* Add (100101)2 and (1101111)2

1001011

```

2. Binary Subtraction:

31(812-11) = 3(603.801) %

Hereacona of the color of the accordance in

0-0=0

0-1=1, with a borrow of 1

1-0 -0 - 1 has provided to be men the most of assume

total of vectorin

1-1 =0

Substract (111.111)2 from (1010/01)2

1010,010

1 PVI. ppj. 1111 1001 1101

0001010151 11110011101

3. Binary Multiplication:

8 (484 - LE 94) = " (34 - AAE) 40

0×0 = 0

0 + 1 = 0

Strong Anthonoctics, Operations:

1 x 0 = 0

moid iloba promise g

1 x 1 = 1

10 = O+C

Multiply (1101)2 by (110)2

x 1110 1 0 0 0 1 101 = 0+

1) 10 m (10100) 61-A

0000

1 1001001

1 0111 110 11 1

1001119001

```

1 -1 =1

Divide (101101)2 by (110)2

001011

sami de de mo

Representation of Signed no.s.

Two ways of representing signed no-s

- · Sign Magnitude form

- · Complemented form

- → In Sign magnitude form, are additional bit called the sign bit is placed in front of the no. If the sign bit is 0, the no. is +ve, if it is 1, the no. is -ve

### \* Complemented Form

- · 1's Complement

- · 2's Complement

# > 1's Complement Representation

The 1's Complement of a binary number is obtained by changing each 0 to 1 and each 1 to 0.

Ez: Find (1100)2 1's Complement

#### 1100

0011 > 1's Complement

alternated actions to the first terminated and the second second

# > 2's complement Representation

The 2's complement of a binary number is a binary number which is obtained by adding 1 to the 1's complement of a number i.e.

2's complement = is complement +1

Exi- Find (1010)2 24 Complement

### 1010

0 1 0 1  $\rightarrow$  1'x Complement

· perform (1011)2 - (0100)2 using 1's complement method.

1's complement for 0100 is 1011

Subtract (9)10 from (4)10 living is complement method

$$A = (4)_{10} = (0100)_2$$

A < B

1's complement for 1001 is 0110

Derform (9)10 - (5)10 using 9's complement method.  $A = (9)10 = (1001)_2$   $B = (5)10 = (0101)_2$ 1's complement for 0101 is 1010

+ 1

2's complement < 1011

DI 100 Discard carry.

perform (4)10 - (9)10 wing the 2's complement method.

A=(4)10=1(0100)2

B= (9)10 = (1001)2 (0010) = 0(1)

2's complement for 1001 is 0111

0100

Add - 45.75 to +87.5 using 12 bit arithmetic +87.5 = 01010111 .1000 -45.75 = 110 10010 -0100 7 21 Complement DO0101001.1100 at a Broth to Manager of the British 9's Complement & 10's complement \*9s complement of 3465 and 782.54 Profi 999.99 1 Design posts 300 11 9999 6534 217.45 11 11000 2011 101 Complement of 4069 is pp.pr x. 9999 P1.000 - 4069 5930 -> 9/2 complement 5 93 d -> 10's complement · Subtract 745.81-436.62 using q'i complement gir complement 999.99 745-81 745.81 - 436 . 62 71436-62 + 563.37 563.37 -> 9's Complement 309.19 B309.18 309 .19 paris simple

part and

· Subtract using q's complement 436-62 - 745.82

9's complement for 745.82 is 999.99 -745 . 82 25417

If no carry result in -ve If it has carry it is the Presult in g'a complement 690.79

Subtract 2928.54 - 416.73 Using 10's complement

18.34 2928.54 19583.27 Do 511.81 4) Ignore carry

9's complement for 416.73 999.99

Discussiques)

やるもだい

OEPA

-0416.73 9583.26

9583.27

10'x compleme

### Subtract 416.73-2928.54 using 10% complement

0416.73

- 2928.54

- 2511.81

0416.73

- 10'A complement for 2928.54 is

$$-2928.54$$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2928.54$

$-2$

# Binary Coded Decimal (BCD)!

right to left represents weights equal to some specialled value and to get the equivalent decimal number add the products of the weights by the corresponding binary digit. 8421 is the most common because 8421 BCD is the most natural amongst the other possible codes.

| Decimal   | BCD  | - Decimal | BCD       |

|-----------|------|-----------|-----------|

| 11600 mod |      | 18        |           |

| 1         | 0001 | 12        | 0001 0001 |

| 2<br>3    | 0010 | 613       | 0001 0011 |

| 1.        | 0100 | 0.6014    | 8 1       |

| 6         | 010  | 1000 I    | 4 1       |

| 4050 9    |      | 1000 1000 |           |

| 8         | 1000 | 1110 1000 |           |

```

* BCD Addition:

cover! Sum is equal or less than 9 and carry is 0.

perform BCD addition of (2)10 and (6)10

(2),0 -> BCD

(6)10 -> 0110

FI DUID

good of the second

1000 -> Sum is a valid

Pronumber.

case 2: Sum greater than 9 but carry =0

perform BCD addition of (7) wand (6) 10

the transfer services to the to the to the total the transfer of the total to the total to

blue cannot be a property decired and the street of the second of the second s

13 Anvalid BCD.

70110 + add 6 to Invalid

act noticed cooling the ood possible color

0001 0011 -> valid BCD.

Case 3: Sum less than or equal to 9 but carry =1

Perform BCD addition of (9)10 and (8)10.

1100 109 -> 1001

1100

+8 ->+1000

0010

1 0001 -> Valid BCD Sum

one and carry=1

1

0001 0001 -> Incorrect BCD result

· Add +6 to

0110 0000

Incorrect BCD

0111 -> Correct BCD

0001

resut

```

7

Add (569)10 and (687)10 in BCD

$$569 \rightarrow 0101 0110 1001$$

$+687 \rightarrow 0110 1000 0111$

$1256$

$1011 1111 0000$

$1000 0111$

$1256$

$1011 1111 0000$

$1000 0111$

$1000 000$

$1000 0111$

$1000 000$

$1000 0111$

$1000 000$

$1000 0111$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

$1000 000$

Add (0110): to Invalid BCD number to get correct

\* BCD Subtraction:

13-0-1

100

to the

Substract (38)10 and (15)10 in BCD

$$38 \rightarrow 0011 1000$$

$-15 \rightarrow -0001 0101$

$0010 0011 \text{ Valid BCD}$

1000 0110 allost

la sin

801

0100010

1

· (206.7)10 - (147.8)10 in BCD 1001 0110 1010 P PD P 206.7 → 0010 0000 0110 . 0111 0100 0111 . 1000 borrow -147.8 · 0001 1011 1110. 1111 0000 from the 1 1311 30 heat gra 0110 · 0110 · 0110 Subtract Valid -> 0101 1000. 1001 with BCP BCP (0110)2 . perform (83)10 - (21)10 using 9'11 complement method q's complement for al is 0110 1010 0110 1010 0100 1000 1000 0011 → + 0111 1000 tito Subtraction 1101 1111 Invalid I Invalid 11(88) BCD BCD 0001 1100 - 88 111100000 - 4 31-01101001000 0001 that in 0110 0001 acld' 01100010 LSB Correct BCD

perform  $(54)_{10}$  –  $(22)_{10}$  in BCD using 10% complement method 10% complement for 22 is 99

77,  $\rightarrow$  9% comp

BCD

54  $\rightarrow$  0101 0100

78  $\rightarrow$  +0111 1000

1100 1100  $\rightarrow$  Anvalid BCD

49nore  $\leftarrow$   $\bigcirc$  0011 0010  $\rightarrow$  Valid BCD

comy

#### Excess-3 (xs-3) code:

It is a non-weighted BCD code Each binary codeword is the corresponding 8421 codeword plus 0011 (3). It is a sequential code & therefore can be used for arithmetic operation.

Decimal digit Excen-3 Code 1 0 1 1 0 0 1 1 man 1 0 1 man 1 Bushy 1 1000 1000

\* Excess-3 Addition

To perform Excess-3 addition, we have to

· Add two excess-3 numbers.

If carry=1 → add 3 to the sum of two cligits =0 → subtract 3

consol draw new roll

\* Ences - 3 Subtractions and both piols wor on it

To perform Exces 3 subtraction, we have to

- · Complement the subtrahend of the state land and the

- · Add complemented subtrahend to minuend

- · If carry = 1, Result in +ve. Add 3 and end around carry.

Grany = 0. Result is -ve, subtract 3.

Ex1- 8-5 \*59 code

8 -> 100110

5 -> 1000 Complement

0101

(19/20) (E em) E (190)

perform the Subtraction (645)10 - (319)10 in 45-3 cocke using the q's complement.

9's complement for 319 is 999 319 680

XS-3 Code → 1001 0111 1000 680 -> 1001 1011 0011 D 0011 0010 1011 +0011 +0011 -0011 0110 0101 1000 <del>></del>41

> 01011001 0110

18 A C . (1) ( now ) ar avoid we not do not to be impressed on the

show years or incl

pur a format of the or

Gray Code

Gray code is a special case of unit-distance code In unit-distance code, bit patterns for two consecutive numbers differ in only one bit position. These codes are also called cyclic codes.

\* BINARY - TO - GIRAY CONVERSION: -

If an n-bit binary number is represented by Bn, Bn-1-B, and its gray code equivalent by Gn, Gn-1---- G1.

Where Gin and Bin are the MSBs. Then gray code bits are obtained from the binary code as follows.

Gin = Bn 1 pm

Gn-1 = Bn & Bn-1

Gi = Ba &BI

Where the symbol of stands for Exclusive OR (X-OR)

Exi- 1001 to Gray code

Biray  $\rightarrow 1 \xrightarrow{\oplus} 0 \xrightarrow{\oplus} 0 \xrightarrow{\oplus} 1$

The gray code for (1001)2 is 1101

| Decimal | Birany | Gray |

|---------|--------|------|

| O       | 0000   | 0000 |

|         | 0001   | 0001 |

| 2       | 0010   | 0011 |

| 3       | 0011   | 0010 |

| 4       | 0100   | 0110 |

| 5       | 0101   | 0111 |

| 6       | 0110   | 0101 |

| 7       | 0111   | 0100 |

| 8       | 1 000  | 1100 |

| 9       | 1001   | 1101 |

| to      | 1010   | 1111 |

| 11      | 1011   | 1110 |

| 12      | 1100   | 1010 |

| 13      | 1101   | 1011 |

| 14      | 0111   | 1001 |

| 15      | (11)   | 1000 |

# \* GRAY - TO - BINARY CONVERSION:

If an n-bit gray number ix represented by

Gn Gn-1. --- G, and its binary equivalent by Bn Bn-1 --- B1,

Then binary bits are obtained from Gray bits as follows.

Bn = Gn

Bn-1 = Bn @ Gn-1

B1 = B2 + G1

# Ext. Convert the gray code 1101 to binary

Gray Binary -OHT

The binary code is 1001

0001

10 - BUNKY CONVERTIONS

111

the property of the time have diller in the The has put the environ promise of the after a tent of and the state good and tomade and state provider in the

1111

(1) 1981

1.11 1 18 18

in the all

### Logic Gates

· Logic gates are the fundamental building blocks of digite systems.

There are 3 basic types of gates AND, OR and NOT. Logic gates are electronic circuits because they are made up of a number of electronic devices and components. Inputs and outputs of logic gates can occur only in 2 levels. These two levels are termed HIGH and LOW, or TRUE and FALSE, or ON and OFF or Simply 1 and 0.

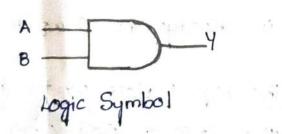

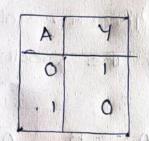

### AND Gate

on AND gate has two or more inputs but only one output. The output is logic 1 state only when each one of its puts is at logic 1 state.

the output is logic o state even if one of its inputs is at Truth Table

logic o state

|    | Inpu | its | output |  |  |

|----|------|-----|--------|--|--|

| 17 | A    | B   | Y=A.B  |  |  |

|    | 0    | 0   | . 0    |  |  |

| 1  | 0    | i   | : 0    |  |  |

|    | -1-1 | 0   | 0      |  |  |

|    | 215  | 1   |        |  |  |

100 00 1

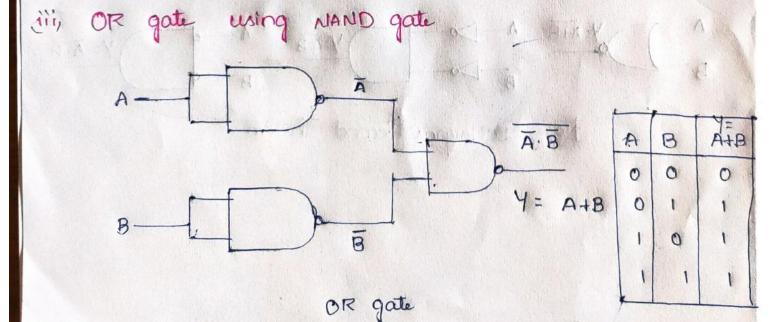

OR Grate:

· An OR gate may have two or more inputs but only one output.

The output is logic 1 state, even if one of its input is in logical state to the solution of

The output is logic o state, only when each one of its inputs is in logic 1 state

Logic Symbol

indicate Hell bonies acom B Y O HO HAN HO

to be a second of the state of the contract of

The property of the second wife.

| Inpu | its | Output  |

|------|-----|---------|

| A    | B   | 4 = A+B |

| 0    | 0   | 0       |

| 0    | t   | 1       |

| , 1  | 0   | 1       |

| 1    | 1   | i       |

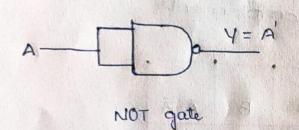

### NOT Gate

- in it into · A NOT gate, also called an Inverter, has only one input and one output.

- It is a device whose output is always the Complement of its input.

- . The output of a NOT gate is the logic 1 state when its input is in logic o state and the logic o state when its inputs is in logic 1 state.

Legic Symbol

Truth Table

| Input | Output |

|-------|--------|

| A     | Ā      |

| O     | 1      |

|       | 0      |

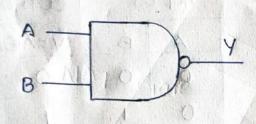

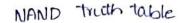

- · NAND gate is a combination of an AND gate and a NOT gate

- The output is logic 0 when each of the sinput is logic 1 and for any other combination of inputs, the output is logic 1.

Logic Symbol

Truth Table

| INPUT |    | OUTPUT |  |

|-------|----|--------|--|

| А     | В  | Y= A·B |  |

| 0     | 0. | 1//1   |  |

| 0     | 1  | 1      |  |

| 1/4   | 0  | 1 1    |  |

| /1    | I. | 0      |  |

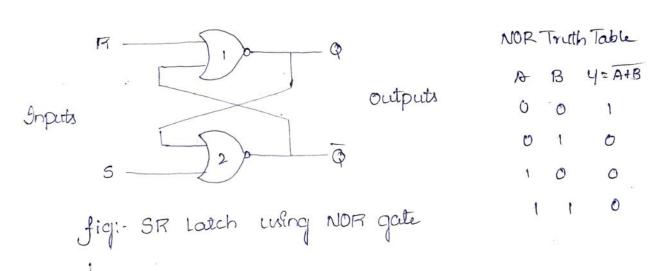

NOR Gate

- · NOR gate is a combination of an OR gate and a NOT gate.

- The output is logic 1, only when each one of its support is logic 0 and for any other combination of inputs, the output is a logic o level.

Truth Table

| Innia Carlot |       | VC NW SON | The state of the last of the l |

|--------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Symbol | INE   | PUT       | OUTPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | A     | В         | Y=A+B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A            | 0     | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 0     | 1         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | A Y   | 10        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | \ \ t | 0.1       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

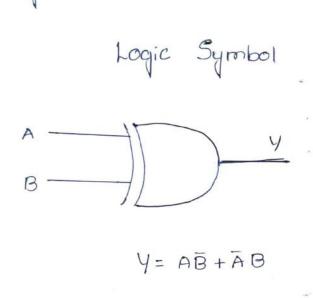

X-OR Gate

An X-OR gate is a two input, one output logic circuit. The output ix logic 1 when one and only one of its two inputs is logic 1. When both the inputs is logic 0 or when both the inputs is logic 1, the output is logic 0.

Truth Table

| INP | JT | OUTPUT<br>Y=A\(\mathbb{B}\)B |  |

|-----|----|------------------------------|--|

| . A | В  |                              |  |

| 0   | 0  | 0                            |  |

| O   | 1  | 1                            |  |

| ı   | 0  | 1                            |  |

| 1   | 1  | 0                            |  |

#### X-NOR Gate

- · An X-NOR gate is the combination of an X-OR gate and a NOT gate.

- · An X-NOR gate is a two input, one output logic circuit.

- The output is logic 1 only when both the inputs are logic 0 or when both the inputs is 1.

- . The output is logic 0 when one of its puts is

Logic o and other is 1.

Logic Symbol

| 5.00 |     |     |      |   |

|------|-----|-----|------|---|

| A —  | 1   | Via | 4    |   |

| B —  | —// | V=  | AB+Ā | Ē |

|      |     | 1   |      |   |

| 140 | ith | lable  |

|-----|-----|--------|

| INF | PUT | OUTPUT |

| A   | 3   | Y=AOB  |

| O   | 0   | 1      |

| 0   | , 1 | . 0    |

| t   | 0   | 0      |

| ١   | 1   | ١      |

### Boolean Algebra

Boolean Algebra is used to analyze and simplify the digital circuits Because, it uses only the binary numbers, i.e., a and 1, it is also called as Binary Halgebra or logical Algebra

Wash Building.

& 51 (BIN)

#### Boolean Laws

- 1. Commutative law

- 2. AND law

- 3. Amociative law

- 4. Distributive law

- 5. OR law

- 6. Inversion law

### Commutative Law

any binary operation which satisfies the following expression is called as commutative operation.

4) A.B = B.A

(1) A+B = B+A

$$\begin{array}{c} A \\ B \end{array} \longrightarrow \begin{array}{c} Y = A + B \\ \end{array} \Rightarrow \begin{array}{c} Y = B + A \end{array}$$

that with a

the proposition late

Christian (Christian)

| In  | puts * | National States | gy Water | New york |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|-----------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A   | 8      | A·B             | BA       | A+B      | B+A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0   | 0      | 0               | 0        | 0 ,      | , O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0   | ı      | 0               | 0        | 1        | Later of the state |

| 1 1 | O      | 0               | 0        | 1        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| . 1 |        |                 | l i      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

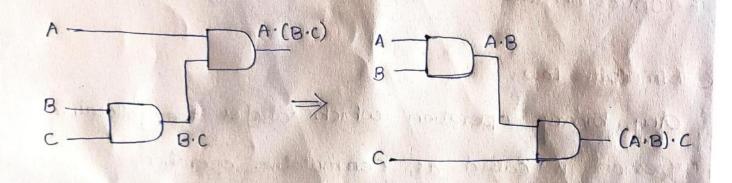

### Associative Law

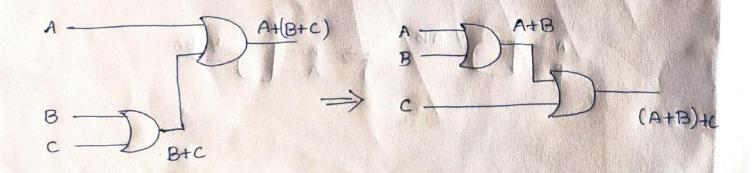

$$(A+B)+C = A+(B+C)$$

| 11 (11.) | upots | No. |     | Am) Ma      |         |  |

|----------|-------|-----|-----|-------------|---------|--|

| A        | 8     | C   | B·C | A·(B·c) A·B | (A·B)·C |  |

| 0        | 0     | 0   | 0   | 10110       | oi i    |  |

| 0        | 0     | 1   | 0   | A O NIN O   | 0, 0    |  |

| 0        | . 1   | 0   | O   | 0 0         | 0       |  |

| 0        | 1     | 1   | t.  | 0 0         | O       |  |

| 1        | 0     | 0   | 0   | 0 0         | 9 110   |  |

| , ,      | O     | J   | 0   | 0           | O       |  |

|          | t     | 0   | 0   | o i         | 0       |  |

| 1        | 1     | 1   | ·   | 1 × 0 × 1   |         |  |

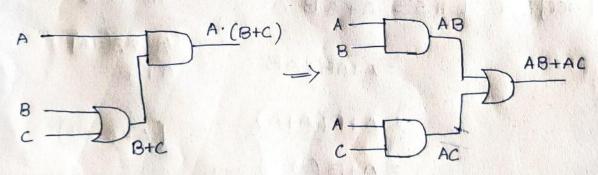

### Distributive Law:

| A | В | I c | B+c | A · (13+c) |    |    |       |

|---|---|-----|-----|------------|----|----|-------|

| 0 | 0 | 0   |     | / Cisa Cy  | AB | AC | AB+AC |

|   | 0 | 0   | 0   | 0          | 0  | 0  | 0     |

| 0 | 0 | 1   | 1   | 0          | 0  | 0  |       |

| 0 | 1 | 0   | I   | 0          | 0  | 0  | e e   |

| 0 | 1 | 1   | 1   | 0          | 0  | 0  | 0     |

| 1 | 0 | 0   | 0   | 0          | 0  | 0  |       |

| 1 | 0 | 1   | 1   | 1          | 0  | 1  |       |

| 1 | 1 | 0   | i   |            | 1  | 0  |       |

| 1 | ı | 1   | . 1 | 1          | 1  | 1  |       |

AND Laws OR Laws Inversion Law \* A.O = 0 \* A+O = A x Af A=0 then  $\overline{A}=1$ ,  $\overline{A}=0$ \* A.I = A \* A+I = 1 (\* 9f A=1 then A=0, A=1 \* A.A = A \* A+A B A \* A+Ā 1 \* A.A = 0 Redundant Laws: i, A+AB=A (Absorption law) Dx00f:-L.H.S = A+AB = A(1+B) (1+B=1) = A(1) Liebral alive Lower = A ii, A+AB = A+B THE RESERVE OF THE STATE OF THE 10800 1: H.S = A+AB (A+AB=A) = A+AB+AB = A+B(A+A) - (A+A(=1) = A+13 (1) DALER BARB (A+B) (A+C) = A+BC Proof: L.H.S = (A+B) (A+C) A.A + AC +B.A + B.C

## Consensus Theorem

W AB + AC + BC = AB+ AC

proof 1- LHS = AB+AC + BC

= AB(1+c) + Ac(1+B)

= AB(1) + AC(1)

= AB + AC

ii, (A+B) (A+C) (B+C) = (A+B) (A+C)

Proof: LHS = (A+B) (A+C) (B+C)

= (AĀ+AC+BĀ+BC) (B+C)

= (AC+BA+BC)(B+C)

= ABC + BB.A + B.B.C + AAC + BAC + B.CC

= ABC+BA+BC+AC+BAC+BC

= AC(1+B) + BA(1+C) + BC

8.B=B C.C=C

A - A = A

ZAB+AC +BC(A+A) = AB+AC+BCA+BCA

MONTH LITTLE A CONTRACTOR

TO A THE STATE OF A

= AA+ BA+AC+BC

= AC+BA+BC

. L. H.S = R. H.S

A+AB = A+B

Proof: LHS = A+AB

= A(B+B) + AB

= AB+AB+AB

= AB+B(A+A)

= AB + B

= A+B

A+AB = A+B

proof: LHS= A+AB

= A(B+B) + AB

= AB+AB + AB (OI)

= AB+ B(A+A)

= AB+B

= A+B

-- [AA = 0]

DELKHARA.

CHS = A + (AB) (: Distributive

(01) = (A+A) (A+B)

= A+B = 12-H-S

( A + AB = A+B)

DOMEST DESCRIPTION

(DEMINE)

LH-S= A+AB)

BAHAR

=(A+A)(A+B)

$=\overline{A}+\overline{B}$

I mansposition theorem;

AB+AC= (A+C) (A+B)

Proof: R-H-5= (A+C) (A+B)

= AA+AB+AC +BC

= 0 + AB+AC+BC

= AB+AC+BC(A+A)

= AB+AC+ BCA+BCA

= AB(1+c)+AC+ABC

= AB+AC+ABC

= AB+ AC (1+B)

= AB+AC

Duality:-

It states that in a two valued Boolean algebra, the dual of an algebra, the dual of an algebraic expression can be obtained simply by interchanging or and AND operators and by replacing 15 by 0s and 0s by 15.

### Given Expression

Qual Expression

0=1

2. 0.1 = 0

3-0-0=0

4. 1.1 = 1

5. A.O = 0

6. A.1 = A

7. A. A = A

1+0=1

1+1=1

0+0=0

A+1=1 0

A+0=A ()

A+A= A

# $A+\overline{A} = 1$ A+B=B+A A+CB+C)=(A+B)+C A+(BC)=(A+B)(A+C) A+AB=A A+A+B=A+B $\overline{A+B}=\overline{AB}$

AB+

$$\overline{A}$$

C +BC = AB+ $\overline{A}$ C

A( $\overline{B}$ +C) = AB+AC

AC+ $\overline{A}$ B = (A+B)( $\overline{A}$ +C)

(AB+CD) = (A+C)( $\overline{A}$ +C)(B+C)

(AB+CD) = (A+C)( $\overline{A}$ +D)(B+C)

(AB+CD) = (A+B)( $\overline{A}$ +B)( $\overline{A}$ +B)

$\overline{A}$ +B  $\overline{A}$   $\overline{A}$

hours designation

# De Morgans Theorem:

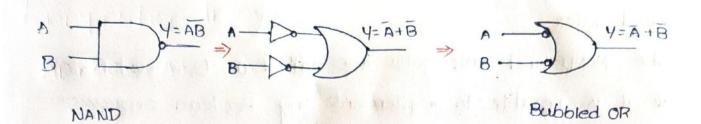

#### Theorem 1: AB = A+B

This theorem states that the complement of a product is equal to addition of the complements.

| 5.no | A | В  | AB | Ā   | B   | Ā + R | 3 |

|------|---|----|----|-----|-----|-------|---|

| •    | 0 | 0  |    | 1   | ľ   | 1     |   |

| 2    | 0 | 1  | 1  | 1 0 | 0   | 1     |   |

| 3    | 1 | 0  | 1  | O   | 100 | 1     |   |

| 4    | 1 | 1. | O  | O   | 0   | 0     |   |

fig: DeMorgania First Theorem

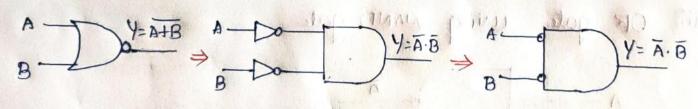

Theorem 2: A+B = A.B

This theorem states that the complement of a sum is equal to the product of complements.

CHAN III

|      | 4.4      | ) !!            | -         | 1         |      |        |              |

|------|----------|-----------------|-----------|-----------|------|--------|--------------|

| 5.no | A -      | В               | A+B       | Ā         | B    | A.B    |              |

| 1    | 0        | 0               | 1         | 10        | 1    | 1      |              |

| 2    | 0        | <b>1</b> , 0, 0 | 0         | 10        | OM   | MOL    | عودات (ایما) |

| 3    |          | 0               | 0         | O         | 1    | 0      |              |

| 14   | 6        | 6               | 0         | O         | 0    | , 0    |              |

| 77   | lith tab | i to            | uerify Do | = Morgan! | s Se | cond t | hoovem       |

Jig: DeMorgan's Second Treorem

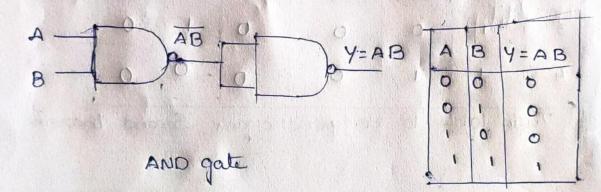

## Universal Grates

The NAND and NOR gater are called on Universal Gates because it is possible to implement any Boolean expression with the help of only NAND or only NOR gates.

Realization of gates using NAND gate

I) NOT gate using NAND gate

in, AND gate using NAND gate

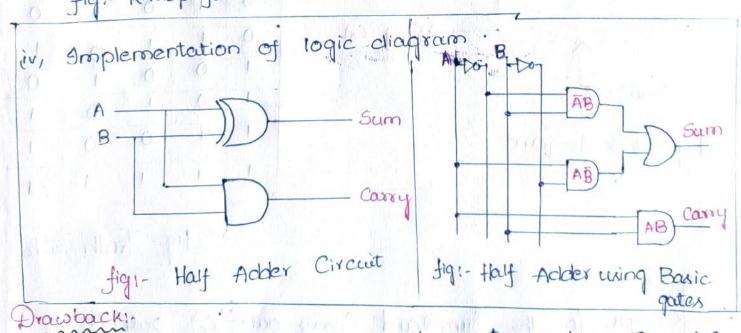

#### Boolean function and Expression:

Y = AB+ AB

Boolean algebra deals with binary variables and logic operations. A Boolean function is described by an algebraic expression called Boolean expression which consists of binary variables, the constants of and I and the logic operation symbols.

WE A NOTE COLD LIVING

EN! - F(A,B,C,D) = A+BC+ADC

Various ways to represent a given function

- 1. Sum of Products form

- · Product of Sums form (MIH) (MIN)

FINE - BRANCHAUMEN - (VIED) (BIND)

mide cm represent are mun.

- This is also called disjunctive counonical form (DCF) or Expanded Sum of products Form or Canonical Sum of products form.

- In this form, the function is the sum of a number of products terms where each product term contains all variables of the function either in complemented or uncomplemented form.

- This can also derived from the truth table by finding the sum of all the terms that corresponds to those combinations for which it assumes the value 1.

Ex: - f(A,B,C) = AB+BC

= AB(C+E)+BC(A+A)

= ABC+ABC+ABC+ABC

- The product term which contains all the variables of the functions either in complemented or uncomplemented form is called a minterm.

- The mintern is denoted as mo, m1, m2 ---

- Another way of representing the function in canonical sop form is the showing the sum of minterms for which the function equals to 1.

for ex:- f(A,B,C) = m1+m2+m3+m6

(or)

f(A,B,C) = \(\int m(1,2,3,6)\)

Where Im represents the sum of all the minterms.

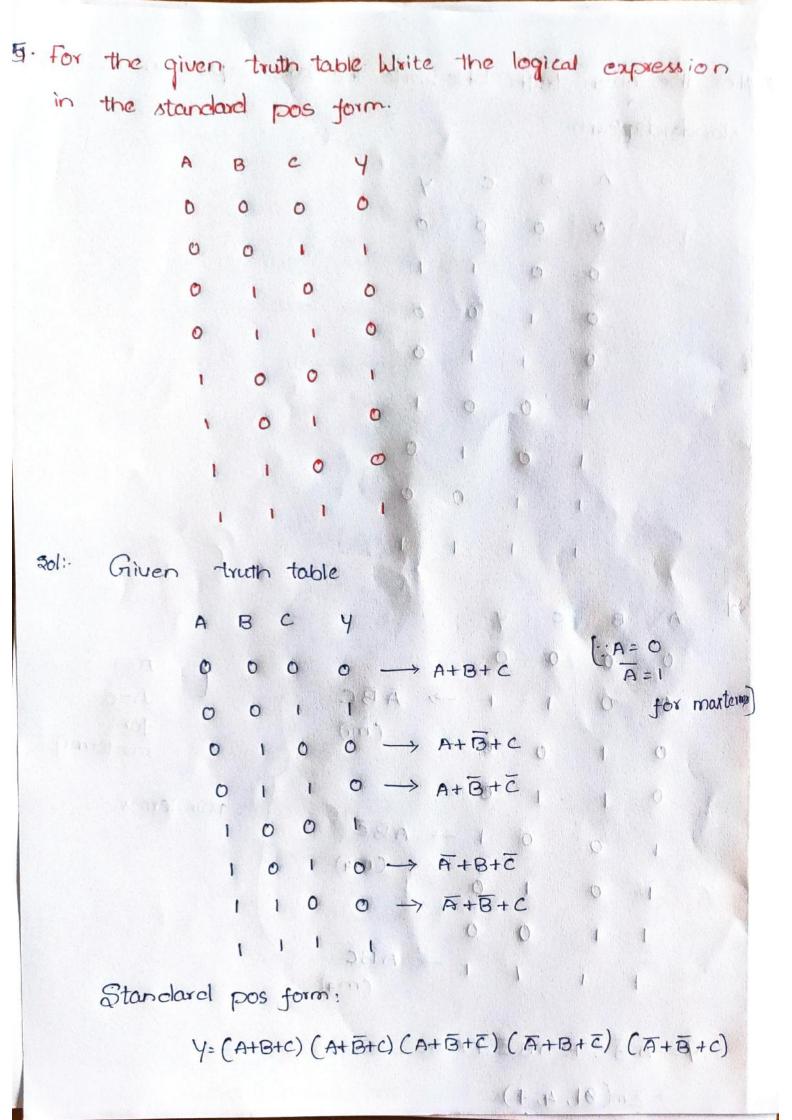

Product of Sum (pos) Forms 1900) Isolomy to mine " This form is also called as Conjunctive Canonical Form or Expanded product of sum form or canonical product of Sums Form.

This is by considering the combinations for which f=0 Each term is a sum of all the variables.

The function f(A,B,C) = (A+B) (A+B)

is main almis

A SHEET WAR

(A+B+C)

The sum term which contains each of the 'n Variables in either complemented or uncomplemented form is called a maxterm.

Maxterm is represented as Mo, Mi, M2 ---

OY

# Sop Standard form

The Complement of a function expressed as the sum of minterms equals the sum of minterms missing from the original function.

= M1 M3 M4 M5 = TTM (1,3,4,5)

1. Expand A (A+B) (A+B+c) to maxterms and minterms

Given pos form ix

A (A+B) (A+B+C)

A = A +(BB)+cc

= (A+B) (A+B) + CC

= (A+B+C) (A+B+C) (A+B+C)

A+B = A+B+CC

= (A+B+C) (A+B+C)

.: A (A+B) (A+B+C)

= (A+B+C) (A+B+C) (A+B+C) (A+B+C) (A+B+C) (A+B+C) (A+B+C)

(A=A·A)

= (A+B+C) (A+B+C) (A+B+C) (A+B+C) (A+B+C) (A+B+C)

= (000)(001)(010)(011)(100)(101)

= Mo. M1. M2. M3. M4. M5

= TM (0,1,2,3,4,5)

The maxterms M6, M7 are missing in the pos form so, the sop form will contain the minterms 6 and 7

= Zm(G,7).

2. Convert the expression into their standard sop form.

Y= AB+AC+BC

Given that 4= AB+AC+BC

= AB(C+E) + AC(B+B) +BC(A+A)

= ABC+ABC+ABC+ABC+ABC+ABC

= ABC + ABC + ABC + ABC

3. Expand A + BC + ABC to maxterms and minterms

Given that Y= A+BC+ABC

= A(B+B)(C+C) + BC(A+A) + ABC

= (AB+AB) (C+E) + BCA+ BCA + ABC

= ABC+ ABC+ ABC + ABC+ ABC+ ABC

= ABC + ABC + ABC + ABC + ABC

= (000) (00 1 1) (01810) (01810) (000) =

= (111)+(110)+(101)+(011)

mi, m6, m5, m4, m3

= Zm(3,4,5,6,7)

Missingminterms are mo, rou, ro 2

So, the maxterms are Mo, MI, M2

= TTM(0,1,2)

3 AFor the given truth table, write the logic expression in the standard apporton.

A B C Y

Y= ABC + ABC + ABC = Σm(81, 4, 7)

# . The property of the second provided and golden 1. Simplify the expression given below Y= AB+ (A+B) (A+B) Given expression in sop form 4= AB+ (A+B) (A+B) = AB+ (AA+AB+AB+BB) SCHEEL SURFIELD OF THE CONTENTS ( AB+AB = AB, BAC BAC PAC 1C A SHEWA AA = O B.B = B) 4= AB+ AB+B =B(A+A)+B (0161A) (5) (1=08+B AAI((Ein8+B=B))()+BIO) liebie - nin 2. Simplify the following three variable Boolean expression.

3 - 5 - 3 A & 3 ( 5 ( 6 ( 6 ) )

4= Zm (2,4,6)

minted (nakana ec Given expression in sop form

[: m2=010

4= m2+m4+m6 10016011601 ABC

my= 100

= ABC+ABC+ABC SIDABUA DALOIGA

ABC

= ABC + AC (B+B) = ABC+AC ABC ABC

= c (AB+A) A+BC=(A+B)(A+C)

= C(A+A) (A+B) = C (A+B)

AND STATE OF THE S

Given expression in pos form

Y= M1. M3. M5 . (-: M1= 00 1

= (A+B+E) (A+B+E) (A+B+E)

6111111 A+B+C = (A+B+c) (AA +AB+AC+BA+BB

+ BC + AC + BC + CC) MS = 110 1

( : AA = 0, CC = C, BB = 0)

BARRAHAN MY (A+B+c) (AB+AC+AB+BC+AC+BC) (CA+B+C)

A+B+2)

= (A+B+c) (AB+c(A+A)+AB+c(B+B)+c)

(: A+Ā =1, B+Ē =1)

= (A+B+c) (AB+C+AB+C+C) 1) = 7 m ( 2 0 . 6 )

= (A+B+c) (AB+AB+c) Green corporation in supplement

010 0 AAB + AAB + AC+ ABB + ABB + BC + ABC + ABC + cc 001

ABC + ABC + ABC = AB+O+AC + AB+O+BC+ABC+BC+OC

= AB + AC + BC + ABC + ABC +C

= AB(I+C) + AC+BC+ABC+C

= AB+AC+BC+ABC+C

$= AB+\overline{c} (A+B+\overline{A}\overline{B}+1)$   $Y = AB+\overline{c}$

(: A+B+AB+1=1)

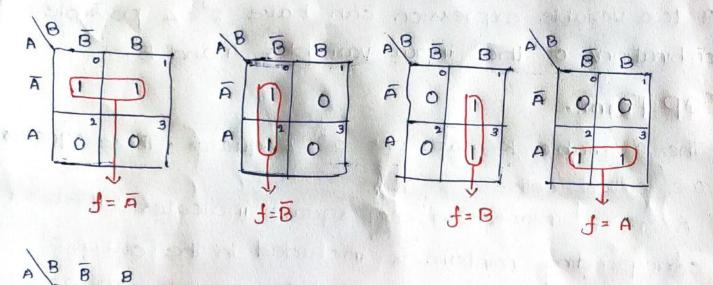

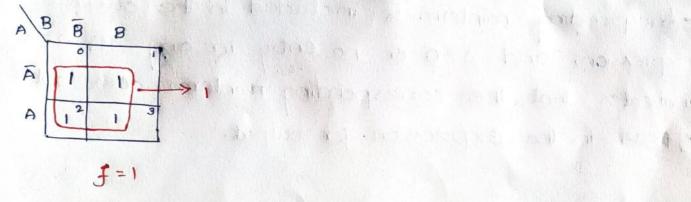

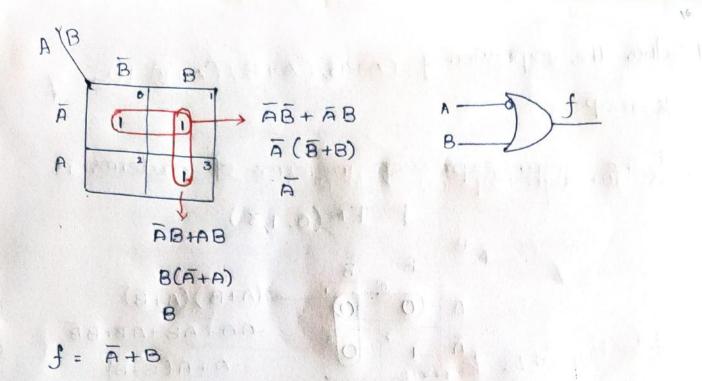

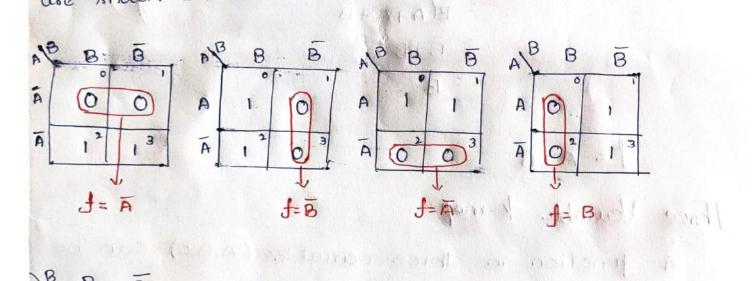

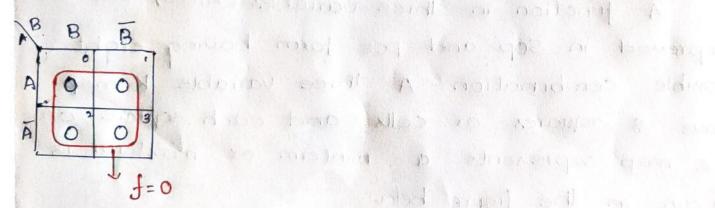

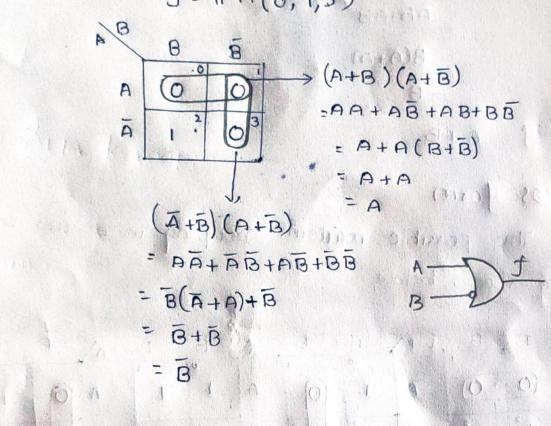

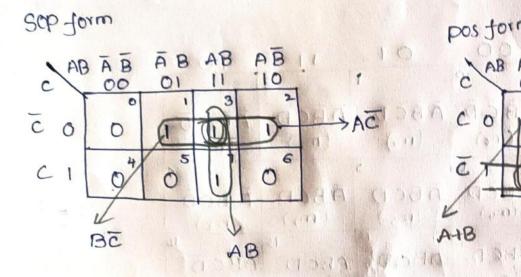

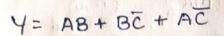

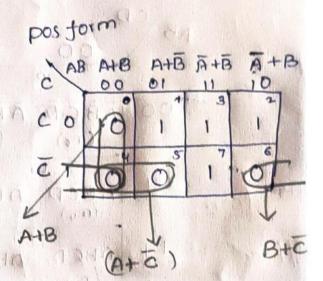

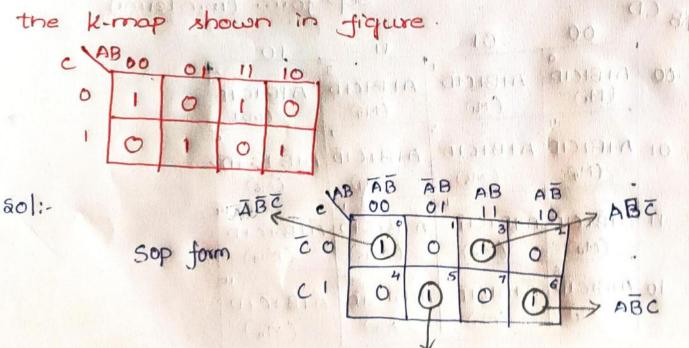

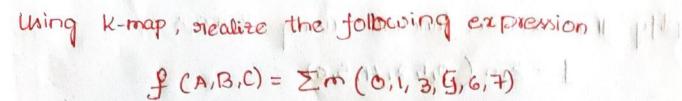

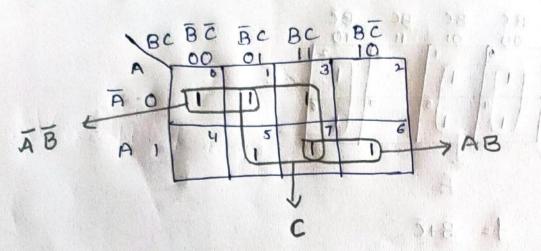

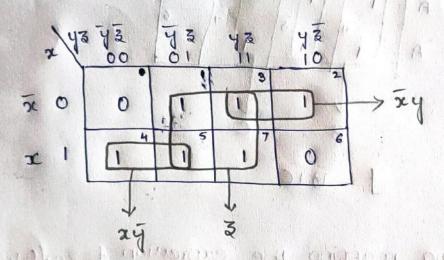

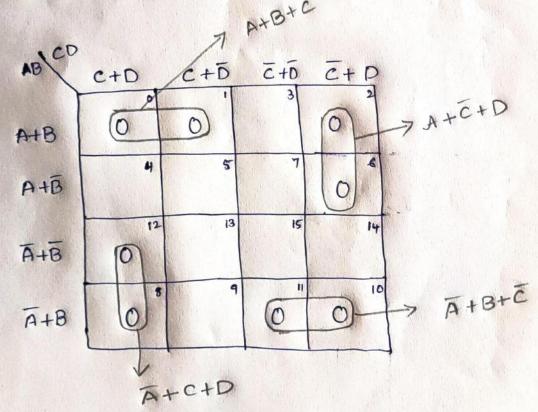

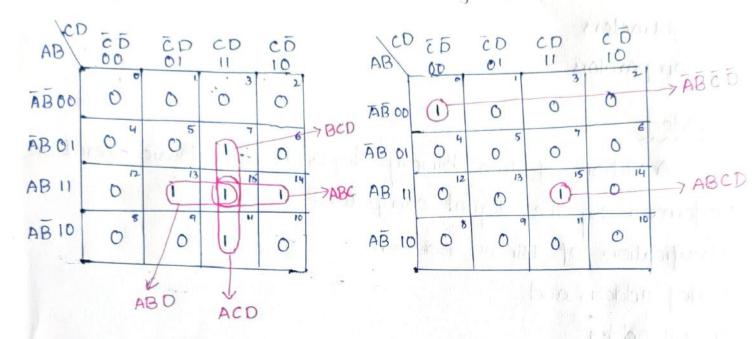

# Karanaugh Maps (ox) K-Maps:

The k-map is a chart or a graph, composed of an arrangement of adjacent cells, each representing a particular combination of variables in sum or product form.

The k-map is systematic method of simplifying the Boolean expression.

King I be a

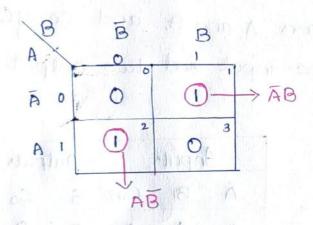

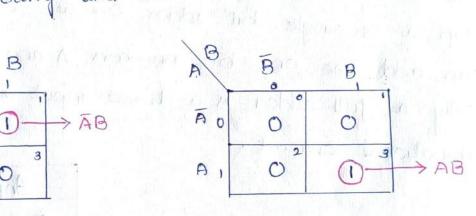

Two Variable k-map:-

A two variable expression can have  $2^2 = 4$  possible combinations of the input variables. A and B.

#### SOP Formi-

- \* The avariable k-map has 22 = 4 squares. These squares are called cells.

- \* A 11 ix placed in any square indicates that corresponding minterm is included in the output expression, and a 0 or no entry in any square indicates that the corresponding minterm does not appear in the expression for output.

| AF | 3 . | 1  |

|----|-----|----|

| 0  | ĀB  | ĀB |

| 1  | AB  | AB |

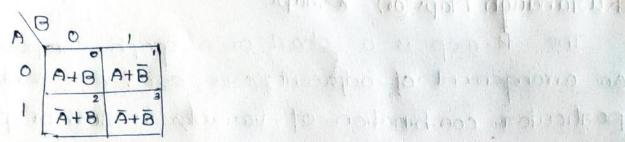

DOS formi-

Each sum term in the standard pos expression is called a Maxterm. A function in two variables (A,B) has 4 possible maxterms, A+B, A+B,  $\overline{A}+B$  and  $\overline{A}+\overline{B}$ . They are

ENTERNATION LANGUE STATE OF THE

Mo, Mi, M2 and M3 respectively. Je presented

Sop Form pinterm grouping in a two variable k-map are shown below

Radiananda Labrada genalia

The property of the property of the party of

Reduce the expression f= AB+AB +AB using L man

Given expression f = AB + AB + AB expressed minterms

Pos form

The possible minterm grouping in a two variable k-map are shown below.

market de la moterna

AND MIN DEN

11999

Reduce the expression f=(A+B)(A+B) (A+B) (Luing K-map

sol: The given expression in terms of maxterms is f = TTM(0, 1,3)

8+A=16

Three Veniable k-map

A function in three variables (A/B,C) can be expressed in sop and pos form having eight possible combination. A three variable K-map have 8 squares or cells and each square on the map represents a minterm or maxterm is

shown in the figure below.

A BC 00 01 11 10

ABC ABC ABC ABC (m) (m) (m) (m)

ABC ABC ABC ABC (m) (m) (m) (m)

Minterms

| 1/ | .00           | 01            | 11            | 10            |

|----|---------------|---------------|---------------|---------------|

| 0  | AHBIC         | A+B+C         | A+B+C<br>(Ma) | AHBIC         |

|    | (Mo)          | 9             | 7             | 6             |

| 1  | A+B+C<br>(M4) | A+B+C<br>(Ms) | AIBIC<br>(Ma) | A+B+C<br>(M6) |

# Four Variable k-map

A four variable (A,B,C,D) expression can have 24=16

Dossible combinations of input variables. A four variable

K-map has 24=16 squares or cells and each

square on the map represents either a minterm

on a maxtern as shown in figure below.

| ABCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Daniel vo    |                   |                    |                   |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|--------------------|-------------------|---|

| A T BINEIN S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00           | 01                | 1118               | 408               | 4 |

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ĀBÇŌ         | ĀBCD              | ABCD               | ABCO              |   |